NEWS

AldecのASICプロトタイピング用FPGAボード「HES-7」がARMのFast Modelと連携可能に

2015年10月27日、論理シミュレータ他、各種ASIC/FPGA設計ツールを手掛ける米Aldecは、同社のASICプロトタイピング用FPGAボード「HES-7」による「ARM Fast Model」のサポートを発表した。

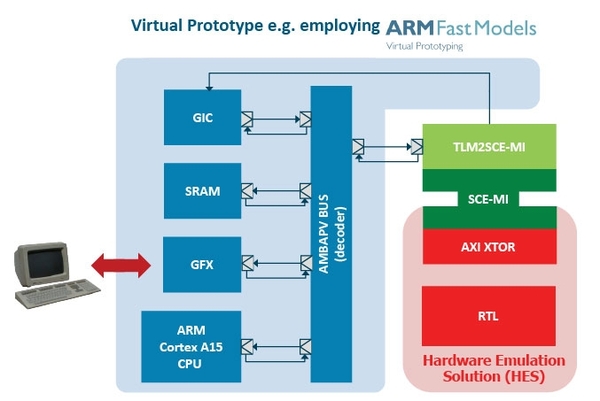

発表によるとAldecはASICプロトタイピング用FPGAボード「HES-7」にARMの Fast Modelと連携させる機能を用意。具体的には、Aldecの用意する検証用IPを利用する事で、「HES-7」上のFPGAに実装されたハードウェア・ロジックとARMの Fast Modelを連携させる事が可能となる。この検証IPには、SystemC TLMアダプタとエミュレーション用のSCE-MIインタフェースに準拠したバス・ファンクショナル・モデルとトランザクタが含まれており、原理的にはARMのFast Modelに限らず外部のSystemCモデルと「HES-7」を連携できる。

※画像はAldec社Web上のデータ

ARMのFast Modelは、ARMがARMベースSoCのソフトウェア先行開発用に提供するバーチャル・プラットフォーム用のプロセッサ・モデルで、実際のARMプロセッサ相当の最大250MIPSでARMの命令を実行する事が可能。その動作の機能的な正確性はARMが保証している。

昨今、ARMベースのSoC開発においては、ARMプロセッサ・モデルをベースとしたバーチャル・プラットフォームとRTLを実装したエミュレーターを連携させるいわゆるハイブリッド・エミュレーション・システムを利用するケースが増えているが、今回Aldecが発表したソリューションはこれと同等のエミュレーション環境を実現する。

コスト・パフォーマンスが高いAldecの「HES-7」とARMのFast Modelを連携させる事で、ユーザーは比較的低コストでハイブリッド・エミュレーション環境を実現する事が可能となり大きな投資が不要となる。また、「HES-7」とのインタフェースがSCE-MIである点も柔軟性の高さという意味でユーザーに歓迎される事だろう。

AldecはXilinxの最新の20nm FPGA Ultrascale-440を搭載するものと、28nm FPGA Virtex-7 2000Tを搭載するもの等、数種類の「HES-7」を用意している。(FPGA搭載個数は選択可能)

|ページの先頭へ|