NEWS

Synopsysがカスタム設計向けの大型新製品「Custom Compiler」を市場投入

2016年3月31日、Synopsysはカスタム設計向けの新ツール「Custom Compiler」のリリースを発表した。

発表によると新製品「Custom Compiler」は、Synopsysの既存のカスタム設計ツール「Custom Designer」と「Laker」それぞれの優れた実績のある技術と、全く新たな自動化技術をベースに構築された新世代のツールで、かつて市場を一変させた幾つかの代表的なツールと同じく「Compiler」を冠した製品名となっている。Synopsysとしても相当気合の入った製品と見て間違いない。

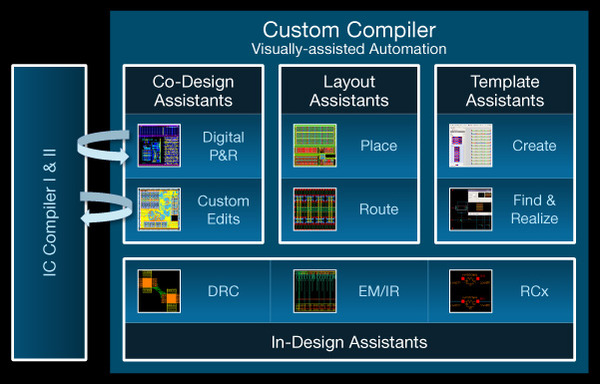

新製品「Custom Compiler」の最大の特徴は、「Visually Assisted Automation」と呼ぶグラフィカル・ベースの新たなカスタム設計自動化技術で、この技術は下記図にある通り大きく4つの自動支援機能によって実現されている。

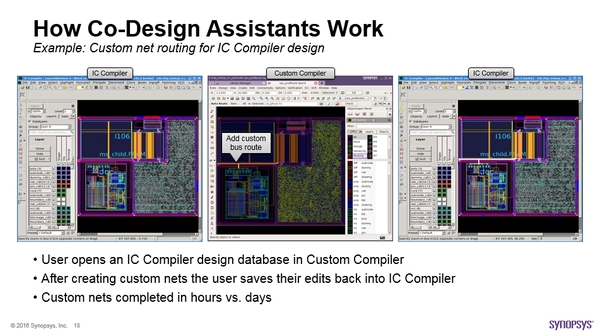

Co-Design Assistantsは、既存の製品と同じくデジタル設計の配置配線ツール「IC Compiler」との協調設計を効率化する機能で、デジタル設計とカスタム設計の間のデータの受け渡しやイタレーションを最少化する。

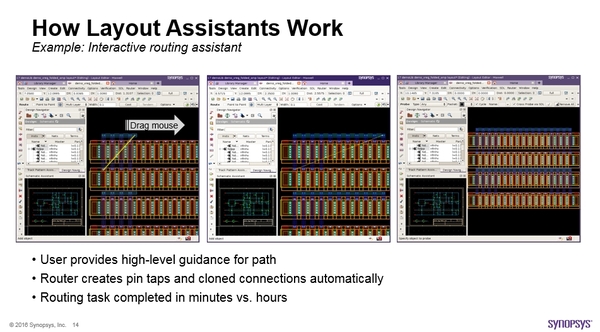

Layout Assistantsは、最新のFinFET技術にも対応するレイアウトの自動化機能で、設計者の意図する配線を自動処理することが可能。この機能は従来必要だったレイアウトに関する制約を記述するという作業を無くし、配線に関する工数を数時間単位から数分単位に削減できるという。

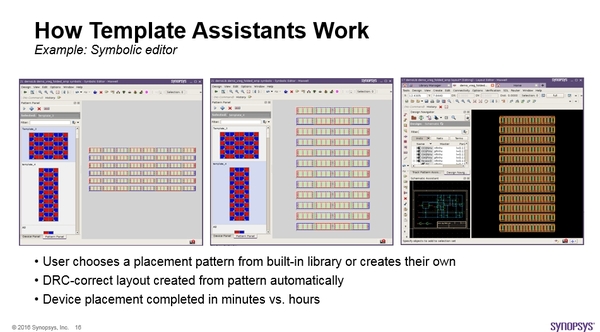

Template Assistantsは、Layout Assistantsと共にレイアウト作業を支援する機能で、予め登録されている汎用的な回路のレイアウト・パターンや、設計者が作成したレイアウト・パターンをテンプレートとして新たなデザインに再利用する事が可能。デザイン資産やノウハウを再利用する事でレイアウトの生産性を大幅に向上させる。

また、Template Assistantsには、「Custom Compiler」で作成したレイアウトを学習する機能が備わっており、既存の設計済回路と類似する回路をに認識し、テンプレートの再利用を賢く効率化してくれる。

In-Design Assistantsは、サインオフ検証前の設計段階でDRCやエレクトロマイグレーション・チェック、寄生容量抽出を行う機能で、搭載される専用エンジンによる事前のエラー・チェックによりサインオフ検証後の手戻りを削減してくれる。エレクトロマイグレーション・チェックと寄生容量抽出については、Synopsysの寄生容量抽出ツール「StarRC」と同じエンジンを使用しているという。(※デザイン容量など制限はあり)

※画像は全てSynopsys社提供のデータ

今回Synopsysが「Custom Compiler」を市場投入してきたモチベーションは、FinFET技術によって現れた新たなカスタム設計の課題解決で、既存製品「Laker」のFinFETレイアウト技術を足掛かりに大胆な自動化アプローチでFinFET市場の攻略を狙っている。カスタム設計ツールの市場はCadenceが長年の間強さを維持しているが、既にTSMCが10nm/7nm FinFETプロセスで「Custom Compiler」を認証するなど、うかうかしていられない状況になってきている。

なお、「Custom Compiler」は正式出荷が開始されており、国内の旭化成エレクトロニクスをはじめとして既に国内外の先行ユーザーによる導入が進んでいる。

|ページの先頭へ|