NEWS

Aldecが一番大きなVirtex UltraScaleとZynqを1個づつ搭載した手頃な新型プロトタイピング・ボードを発表

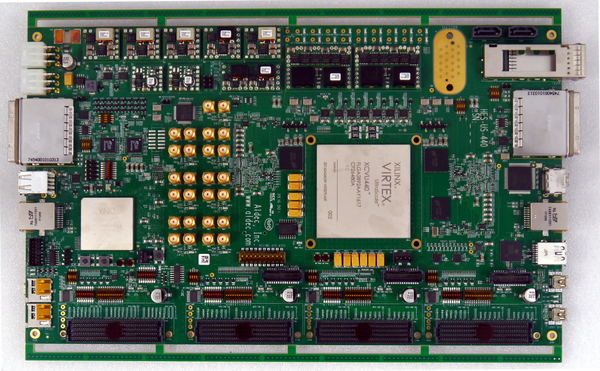

2017年2月28日、論理シミュレータ他、各種ASIC/FPGA設計ツールを手掛ける米Aldecは、新型のプロトタイピングボード「HES-US-440」の発売を発表した。

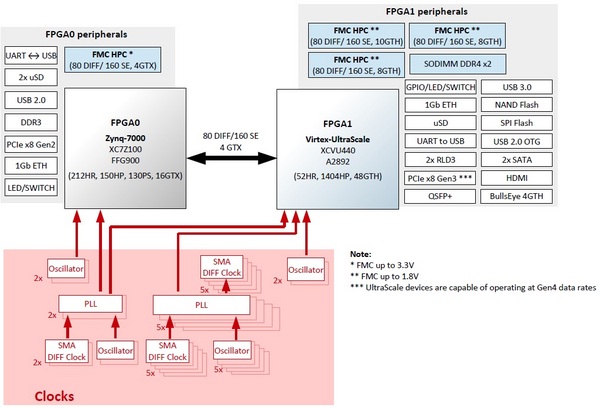

発表によると「HES-US-440」は、Xilinxの20nm FPGA 「UltraScale™」の一番大きな製品「XCVU440」とARM搭載FPGA「Zynq®-7000」の一番大きな製品「Z100」をそれぞれ1個搭載するプロトタイピング・ボードで、デザイン容量は最大2600万ゲート。小-中規模のASICデザインと大規模FPGAデザインのプロトタイピング・ニーズを狙うもの。

同社は既に「UltraScale™」を3個搭載する最大7900万ゲート対応の「HES-US-1320」をリリースしているが、ユーザーからの要望に応え、1つのFPGAでデザインを分割せずに利用できる汎用のデスクトップ・プロトタイピング・プラットフォームというコンセプトで「HES-US-440」を製品化した。

「HES-US-440」上に搭載される「Zynq®-7000」は、ホストコントローラとして利用されるもので、ARMを搭載する「Zynq®-7000」と最大容量の「UltraScale™」があれば、様々なニーズに対応する事が可能。Aldecはその使い方の一例として、自己完結型の埋め込みテストベンチを自分で作成できるようになると紹介している。

AldecのHESボードは、専用のソフトウェア環境「HES-DVM™」を用いることで、プロトタイピングだけでなくシミュレーション・アクセラレーションやエミュレーション・モードも使用できるというのがウリの一つ。当然ながら「HES-DVM™」もバージョンアップされ、新製品「HES-US-440」に対応している。

※画像は全てAldec社Web上のデータ

|ページの先頭へ|