# JEVeC のご紹介

# Japan EDA Venture Consortium

日本 EDA ベンチャー連絡会

2014年11月

# はじめに

日本 EDA ベンチャー連絡会(略称: JEVeC)が設立されてから、8 年が経ちました。日本の半導体業界はこの 8 年の間に様変わりし、様々な企業が M&A や 統廃合を繰り返し今日に至っています。しかし、世界的に半導体の需要そのものは増加しており、JEVeC 設立当時の 2006 年世界半導体出荷額は 2,477 億ドル $^{*1}$  だったのに対し、2013 年は過去最高の 3,056 億ドルと、約 1.2 倍となっています。今後も新たな市場が開拓され、半導体の需要は増々増加していくものと期待されます。

半導体の需要は増加傾向にありますが、その設計や製造方法等は様変わりしています。時代のニーズに対応し、最適なソリューションを如何に提供していくかが、EDAに課せられた使命です。このような時代に於いて JEVeC が担う役割は増々重要になって行くでしょう。

本書は、日本の EDA を支える JEVeC の会員紹介冊子です。各々の得意分野を集結すれば、半導体の設計から製造、品質管理、サービスまでほぼすべての分野を網羅しており、必ずや皆様のお役にたてる事と自負しております。

ご支援のほど、よろしくお願い申し上げます。

2014 年 9 月 JEVeC 副会長 株式会社アストロン 代表取締役社長 中島 義弘

\*1: WSTS (WORLD SEMICONDUCTOR TRADE STATISTICS:世界半導体市場統計)より

# 目次

| 【正会員】                      |    |

|----------------------------|----|

| 株式会社アストロン                  | 1  |

| 株式会社 日立ハイテクサイエンス           | 2  |

| ケイレックス・テクノロジー株式会社          | 3  |

| 株式会社ジーダット                  | 4  |

| 株式会社 NTT データ数理システム         | 5  |

| 株式会社東京システム技研               | 6  |

| TOOL 株式会社                  | 7  |

| 日本電気株式会社                   | 8  |

| 有限会社アートグラフィックス             | 9  |

| 株式会社ジェム・デザイン・テクノロジーズ       | 10 |

| 株式会社Trigence Semiconductor | 11 |

| 日本コントロールシステム株式会社           | 12 |

| プロトタイピング・ジャパン株式会社          | 13 |

| スタビリティ株式会社                 | 14 |

| 株式会社アプリスター                 | 15 |

| 株式会社 ESL 研究所               | 16 |

| 株式会社アナジックス                 | 17 |

| 【賛助会員】                     |    |

| 株式会社半導体理工学研究センター           | 18 |

| 株式会社図研                     | 19 |

| 【学術会員】                     |    |

| 早稲田大学 渡邊 孝博                | 20 |

| 早稲田大学 井上 靖秋                | 21 |

| 中央大学 築山 修治                 | 22 |

| 神戸大学 永田 真                  | 23 |

| 高知大学 村岡 道明                 | 24 |

| (会員番号順)                    |    |

| 日本 EDA ベンチャー連絡会設立趣意        | 25 |

| 会員名簿                       | 27 |

| JEVeC について                 | 28 |

株式会社アストロン

# 事業/製品/サービス/研究内容の概要

弊社は 25 年以上にわたり、半導体業界向けにカスタムソフト開発並びにソフトウエア製品を提供し続けています。設計、レイアウト、テストから解析まで、幅広くソリューションを提案しております。

近年は、蓄積した画像処理技術を用いての画像処理関連ソフトウエアの開発も行っております。半導体業界に限らず、建築・土木、食品、環境等様々な業界・分野にもソフトウエアをご提供しております。

# 【半導体カスタムソフトウエア事例】

- ◇SPICE 関連(ネットリストビューア、チェッカー、抽出等)

- ◇高速 P&R (ASIC、メモリ、LCD 向け)

- ◇レイアウトエディタ

- ◇テスター用カスタムソフト (STIL、VCD、WGL 変換等)

- ◇SEM 画像からのレイアウトエッジ抽出(GDS データ作成)

# 【半導体製品紹介】

- ◇GDSⅡ高速ビューア『SView』

- ◇CAD ナビゲーション『AZSA / NASFA』

- ◇セル、VIA、配線カウンティング『Marrive』

- ◇ネットリスト抽出システム『Neals』

# 【画像処理カスタムソフトウエア事例】

- ◇外観検査 良品/不良品検査システム開発

- ◇輝度値測定システム開発

- ◇ブルーライト測定システム試作(経済産業省プロジェクト)

| 得意分野    | ◎最も得意とする分野           | 〇対応可能分野       | (保有技術を3つまで記入)      |   |

|---------|----------------------|---------------|--------------------|---|

| ()シス    | テム・回路設計/検証           | (保有技術:        |                    | ) |

| (0) レイ  | アウト・マスク設計/検証         | (保有技術:LSI/PCE | 3 P&R、フロアプラン、DRC   | ) |

| (0)パッ   | ケージ・ボード設計/検証         | (保有技術:リードフ    | レーム自動配線、BGA フロアプラン | ) |

| ( )デバ   | イス・プロセス設計/検証         | (保有技術:        |                    | ) |

| ( ) IP• | サービス                 | (保有技術:        |                    | ) |

| (◎) 製造  | <ul><li>検査</li></ul> | (保有技術: 故障解析   | f、CAD ナビゲーション、外観検査 | ) |

| ()その    | 他 ( )                | (保有技術:        |                    | ) |

|         |                      |               |                    |   |

**所在地** 〒160-0023

東京都新宿区西新宿 4-32-12 西新宿フォレスト LB 階 3 号

**電話番号** 03-6304-2181 **FAX 番号** 03-6304-2183

URL <a href="http://www.astron.co.jp">http://www.astron.co.jp</a>

連絡先 ソリューション Gr. プロダクトデザイン Sec.

伊佐 敏 (イサ サトシ) <u>satoshi.isa@astron.co.jp</u>

株式会社日立ハイテクサイエンス

# 事業/製品/サービス/研究内容の概要

株式会社日立ハイテクサイエンス・MDP-Group では半導体マスクレイアウト検証ソフトウェア SmartMRC を開発販売しております。販売開始から 10 年が経ち、アジア地区を主として幅広いマスクショップ、半導体製造メーカに採用されており、MRC ソフトウェアとしてデファクト・スタンダードの地位を占めるまで至りました。

# [SmartMRC の特徴]

- ・分散並列処理を用いた超高速マスクデータ処理

- ・現存するマスクデータフォーマットのほぼすべてについて入力・検証が可能

- ・パターン幅、スペースチェックなどの基本 MRC 機能から、高度な検証機能まで幅広くサポート

- ・他の追随を許さない、高速ファジーパターンマッチングアルゴリズムを搭載

- ・大型 FPD 向けマスクデータ変換・検証ラインナップの充実

これらの SmartMRC 単体の販売ビジネスに加えて、近年 EDA メーカおよび製造装置メーカ向けに、ソフトウェア部品の OEM 提供を始めました。すでに数多くの EDA 製品、製造装置にて日立ハイテクサイエンス製の OEM ソフトウェア部品が動作しております。ご興味のある EDA メーカ様、装置メーカ様はお問い合わせください。

| 得意分野    | ◎最も得意とする分野   | 〇対応可能分野   | (保有技術を3つまで記入)         |   |

|---------|--------------|-----------|-----------------------|---|

| ()シス    | テム・回路設計/検証   | (保有技術:    |                       | ) |

| (◎) レイ  | アウト・マスク設計/検証 | (保有技術:大規模 | マスク・OPC レイアウトデータの高速検証 | ) |

| ( )パッ   | ケージ・ボード設計/検訓 | (保有技術:    |                       | ) |

| ( )デバ   | イス・プロセス設計/検討 | (保有技術:    |                       | ) |

| ( ) IP• | サービス         | (保有技術:    |                       | ) |

| (〇) 製造  | • 検査         | (保有技術:製造・ | 検査装置向けのデータ処理エンジン提供    | ) |

| ()その    | 他 ( )        | (保有技術:    |                       | ) |

|         |              |           |                       |   |

**所在地** 〒105-0003

東京都港区西新橋一丁目 24 番 14 号

**電話番号** 03-3504-3978 **FAX 番号** 03-3504-5189

URL <a href="http://www.hitachi-hitec-science.com/">http://www.hitachi-hitec-science.com/</a>

連絡先 システム開発課 加藤心

kato-kokoro@hhs. hitachi-hitec. com

ケイレックス・テクノロジー株式会社

# 事業/製品/サービス/研究内容の概要

2004年にEDA(電子回路自動設計)のコンサルティング、設計構築サービス、ソフトウエア受託開発の専業企業として設立しました。現在は進歩の激しい IT 技術、データ処理技術、画像処理技術の最先端にも経験を広げ、より高品質なもの作り、業務サービス、システム構築に寄与・貢献を使命とする独立系 IT サービス会社です

# ◆ ソリューションサービス

◇ 各種 EDA ソリューションサービス

エレクトロニクスおよび半導体関連の設計、製造のためのデータ変換、プラットフォーム構築サービスを提供します

◇ 各種 IT ソリューションサービス

EDA プラットフォーム構築に必要なネットワーク組込み、統計解析、数値解析、各種画像処理といった IT 技術のイン テグレーションサービスを提供します

◇ PDK・ライブラリー開発サービス

各種 EDA ツールを使用するために必要なライブラリの生成、変換サービスです

#### ◆EDA および IT 関連製品

◇ SECLANCER(シークランサ): 秘密分散システム

秘密分散法(Secret Sharing Scheme)を応用したデータ保管システムで、設計データや製造データといった企業機密情報を複数拠点に複数ピースに分割且つスクランブルをかけて分散保管するシステムです。いずれかの拠点から単ーピースのデータが事故または不正に流出したとしても元の情報は復元できません

◇ FUJIKO(フジコ)パーサ: 半導体設計/製造フォーマットパーサ

JPCA(日本電子回路工業会)規格 EB-01(部品内蔵基板)、EB-02(部品内蔵基板データ)準拠のデータフォーマット FUJIKO のアクセスパッケージです

# 得意分野 ◎最も得意とする分野 ○対応可能分野 (保有技術を3つまで記入)

- (O) システム・回路設計 (保有技術:ツールフロー構築,ツール評価,データ変換)

- (O) レイアウト・マスク設計 (保有技術:ツールフロー構築, MDP, データ変換, データベース設計)

- (O) パッケージ・ボード設計(保有技術: CAE 環境構築 , データベース設計 , データ変換 )

- ( ) デバイス・プロセス設計/検証(保有技術: )

- (O) IP・サービス (保有技術:キャラクタライズ , CAA , ターンキー支援)

- (〇)製造・検査 (保有技術:画像処理 , 業務フロー構築 , DFM/DFT 構築 )

- (◎) その他 ( IT デザインサービス ) (保有技術:インターネット構築サービス , データベース設計 )

**所在地** 〒104-0042

東京都千代田区入船 1-1-26 永井ビル 7F

**電話番号** 03-3537-1925 **FAX 番号** 03-3551-7622

URL http://www.keirex.com

連絡先 担当者名・メールアドレス : keirex-support@keirex.com 営業部宛

株式会社ジーダット

# 事業/製品/サービス/研究内容の概要

ジーダットは、半導体(LSI)や液晶(LCD)パネルの設計に不可欠な EDA(Electronic Design Automation)ソフトウェア の研究開発型カンパニーです。回路・レイアウトの設計ツールや数値シミュレーションツールなどを自社開発しています。

当社は2004年にセイコーインスツル株式会社(SII)から分離独立して設立された、EDA事業では30年以上の経験を持つ会社です。無借金かつ高い自己資本比率を維持した安定した経営を行い、研究開発や社員のスキルアップにも力を入れ、高度な技術に挑戦し続けています。

当社では、様々な国籍の優秀な社員が世界を視野に入れた製品開発を行っています。2005 年には中国・北京市に R&D 子会社を設立して開発を強化するとともに、世界中の優れた EDA 企業と提携し、フォーカスする分野で先行する技術を取り込んで、より価値のあるソリューションを創造しています。

# ◆ EDA 製品

◇ α-SX 一統合型電子デバイス設計環境 –

アナログ LSI、パワー半導体、センサー、FPD(Flat Panel Display)、MEMS(Micro Electro Mechanical Systems)等、各種電子デバイスの設計を強力にサポートします。回路設計からレイアウト検証までのトータル設計フローをカバーして、マニュアル、自動、半自動等の多様な設計手法に幅広く対応しています。また最近では特に携帯機器向けのデバイス設計に不可欠な、各種解析機能の強化に取り組んでいます。

◇ HOTSCOPE 一大規模マスクデータ対応 解析ブラウザー

テラバイト規模の大規模な設計データ、マスクデータを高速にオープンし、表示倍率に関わらず高速・高品質に表示します。最近の機能拡張では、各種の解析機能を実装し、増加しつづける大規模 LSI データのチェック効率を大幅に向上させることを目指します。

◇ Cforce ー高速・高精度アナログ回路シミュレーター

アナログ回路の定数最適化およびばらつき解析に最適な、ベストコストパフォーマンス回路シミュレータです。業界トップ クラスの実行速度を達成し、汎用回路シミュレータとの互換性を提供しています。疑似過渡解析技術により安定でかつ高い 収束性を確保しつつ、高精度ソルバ技術により高精度シミュレーションを実現します。

| 得意分野           | ◎最も得意とする分野   | 〇対応可能分野 (保有技術を3つまで記入)            |   |

|----------------|--------------|----------------------------------|---|

| (O) シス         | テム・回路設計/検証   | (保有技術:高速回路シミュレーション技術、並列処理技術      | ) |

| (◎) レイ         | アウト・マスク設計/検証 | (保有技術:高速物理データ処理技術、電気的特性高精度抽出解析技術 | ) |

| ( ) パッ         | ケージ・ボード設計/検証 | (保有技術:                           | ) |

| ( ) デ <i>バ</i> | イス・プロセス設計/検証 | (保有技術:                           | ) |

| ( ) IP•        | サービス         | (保有技術:                           | ) |

| ( )製造          | •検査          | (保有技術:                           | ) |

| ()その           | 他 ( )        | (保有技術:                           | ) |

|                |              |                                  |   |

| <b></b> | <b>⊤</b> 103-0004 |

|---------|-------------------|

|         |                   |

東京都中央区東日本橋 3-4-14 OZAWA ビル

**電話番号** 03-5847-0312 **FAX 番号** 03-5847-0315

URL <a href="http://www.Jedat.co.jp">http://www.Jedat.co.jp</a>

**連絡先** 東京営業所: <u>03-5847-0313</u> 西日本営業所: <u>06-6150-0930</u> Email: <u>pergunta. 2008@jedat. co. jp</u>

(株) NTT データ数理システム

# **NTT Data**

NTT DATA Mathematical Systems Inc.

# 事業/製品/サービス/研究内容の概要

当社は、創業以来、一貫して、シミュレーションを中心とする科学技術計算、特に、TCAD(プロセス、デバイス、回路シミュレータ)を中心とした半導体の設計ツールの開発に携わってきました。最近では、MEMS の機械機構と LSI の制御回路との連成解析ツールも開発しました。

当社は高速線形計算(マトリクス計算)、並列計算など、高速演算に抜群の強みを持ち、それを利用して、比類のない高速度計算、高精度計算、大規模計算を達成しております。また、当社が得意とする数値的最適化計算を利用して、各種シミュレータのパラメータ最適化ツールも開発しております。

# [製品案内例]

- O 3次元LSI形状シミュレータ ParadiseWorld-2

- ➤ マスクレイアウトパタンとプロセスレシピから、Voxell モデルと独自のプロセスモデル計算式により、 広範囲の3次元LSI形状を精度よく生成する。

- ▶ 生成されたパタンから配線を自動的に抽出し、寄生の容量、抵抗、インダクタンスを有限差分法により他に類を見ない高速度かつ高精度で計算する。

- ▶ Voxell 形状から他の CAD 形状ファイルに変換し、ANSYS など他のシミュレータへの連携が可能である。

- O MEMS 回路連成解析ツール MEMSpice

- ➤ MEMS の機械解析とその制御電子回路を含めて同時に動作解析を行う、これからの MEMS 技術者に書くこと のできないツールです。

- ▶ パラメータ最適化機能と、有限要素解析結果からのマクロモデル抽出機能をもつ。

- 高速線形回路シミュレータ LiCRSIM

- ▶ LRC および各種電源からなる超大規模線形回路を Spice の数百倍の速さで解析する。電源網などの解析に 最適である。大規模寄生インダクタンスを含む回路が解析できる唯一のツールである。

- O SPICE ネット圧縮ソフトウエア Thyme

- ▶ 大規模ディジタル回路から検証に必要な部分だけを取り出し、回路規模を大幅に圧縮する。

| 得意分野   | ◎最も得意とする分野   | 予 〇対応可能分野          | ・野 (保有技術を3つまで記入)      |   |

|--------|--------------|--------------------|-----------------------|---|

| (0) シ  | ステム・回路設計/検証  | (保有技術:線用           |                       |   |

| ( ) レ  | イアウト・マスク設計/樹 | <b>註(保有技術:</b>     |                       | ) |

| ( ) パ  | ッケージ・ボード設計/樹 | <b>註(保有技術:</b>     |                       | ) |

| (◎) デ  | バイス・プロセス設計/村 | è証(保有技術:高 <b>遠</b> | i速3D 形状作成、3D−DR チェック) |   |

| ( ) IP | ・サービス        | (保有技術:             |                       | ) |

| ( )製   | 造・検査         | (保有技術:             |                       | ) |

| (0) そ  | の他(          | )(保有技術:デ           | データマイニング、汎用最適化)       |   |

|        |              |                    |                       |   |

|        |              |                    |                       |   |

**所在地** 〒160-0016

東京都新宿区信濃町 35 番地 信濃町煉瓦館 1F

**電話番号** 03-3358-1701 **FAX 番号** 03-3358-1727

URL <a href="http://www.msi.co.jp">http://www.msi.co.jp</a>

連絡先 水田 千益 (みずた ちえき) <u>mizuta@msi.co.jp</u>

株式会社 東京システム技研

# 事業/製品/サービス/研究内容の概要

当社は、東京エレクトロン(株)のソフトウェア事業部門として生まれ、(株)東京放送[TBS]の協力を得て昭和46年に独立しました。設立当初よりシステムソフト開発を手掛ける一方、EDA(Electronic Design Automation)分野ではいち早くパッケージの輸入販売を始めるなどソフトウェアの基盤技術から最先端技術まで幅広く展開してきました。

- ●サーバーコンピュータにおける基盤ソフトウェア開発、及びテクニカルサポート

- ・サーバーコンピュータの OS と製品の開発

- ・マルチプラットフォームでのミドルウェアの開発

- ●インフラ構築・運用、組込みソフトウェアの開発・検証・技術サポートと、ECAD システムの開発

- ・インフラ構築から運用まで

- ・各種サーバー向けドライバ開発・検証・技術サポート

- ・プリント基板設計用CADシステムの開発

- ●エンドユーザ向けの業務ソリューションとパッケージソリューションの提供

- ・金融系コールセンター向けアプリケーションの提供

- ・生産管理系パッケージの導入分析、カスタマイズ開発、導入支援の提供

- ・業務データベースの構築、最適化、維持運用、保守

- ●スマートフォン/タブレット型多機能端末とクラウドコンピューティングを活用したソリューション/サービスの提供

- ・スマートフォン/タブレット型多機能端末向けシステム企画とソリューション提供

| <b>得意分野</b> ◎最も得意とする分野 | 〇対応可能分野 (保有技術を3つまで記入) |   |

|------------------------|-----------------------|---|

| (○) システム・回路設計/検証       | (保有技術:フロアプランナーツールの開発  | ) |

| ( ) レイアウト・マスク設計/検証     | (保有技術:                | ) |

| (◎) パッケージ・ボード設計/検証     | (保有技術:プリント基板統合ツールの開発  | ) |

| ( ) デバイス・プロセス設計/検証     | (保有技術:                | ) |

| ( ) IP・サービス            | (保有技術:                | ) |

| ( )製造·検査               | (保有技術:                | ) |

| ( )その他( )              | (保有技術:                | ) |

|                        |                       |   |

**所在地** 〒160-0023

東京都新宿区西新宿 1-21 明宝ビル

**電話番号** 03-3342-1144 **FAX 番号** 03-3342-2621

URL <a href="http://www.tsl.co.jp">http://www.tsl.co.jp</a>

連絡先 テクノロジーシステム部 市川幸男

sachio@tsl.co.jp

TOOL 株式会社

# 事業/製品/サービス/研究内容の概要

1970 年に株式会社トウール社として創業を開始し、2002 年に TOOL 株式会社を設立。電気系 CAD ツールから EDA (Electronic Design Automation:電気系設計作業の自動化支援)ツールまで、長年に渡り半導体の設計に関連したツールの開発および販売を行っています。

また、EDA ツール開発技術に加え、IP(画像処理)分野や ES(組込システム)分野における豊富な経験を活かした「開発サービス」も行っています。お客さまのご要望にお応えしながら仕様の検討から設計、開発、サポートを行い、お客様の問題解決に的確なソリューションをご提供しています。

#### ◆ EDA 製品

# **♦ LAVIS-plus**

レイアウト設計データを高速に読み込み表示する LAVIS-plus は、ビューアとしての用途に加え、電気特性解析や検証エラー表示、簡易編集なども行える「IC デザイン視覚検証システム」として、設計から検証、マスク製造、検査、不良解析に至るさまざまな工程でご活用いただけます。

# **♦ OASIS-Utility**

OASIS のデータ操作や OASIS と GDS、OASIS とテキストデータとの相互変換、セルの階層展開、フォーマットおよび制限チェック、DUMP 出力、階層情報のリスト出力などといった、OASIS データ処理に有用な機能を備えた「OASIS データハンドリングツール」です。

# **♦ RSCALC**

電源 PAD などからの抵抗値や指定した2点間の抵抗値に加え、電流密度や電流値、電位などの計算も可能な「高速抵抗値計算&解析ツール」です。計算結果はカラーマップ(分布図)として「LAVIS-plus」上に表示することもできます。

#### ♦ MaskStudio

レイアウト設計データを最新のマスク技術に対応した描画データに超高速かつ高品質に変換する「フラクチャリングシステム」です。

| 得意分野 ◎最も得意とする分野    | 〇対応可能分野 (保有技術を3つまで記入)             |   |

|--------------------|-----------------------------------|---|

| ( )システム・回路設計/検証    | (保有技術:                            | ) |

| (◎)レイアウト・マスク設計/検証  | (保有技術:高速物理データ処理技術、電気特性抽出技術、並列処理技術 | ) |

| ( ) パッケージ・ボード設計/検証 | (保有技術:                            | ) |

| ()デバイス・プロセス設計/検証   | <b>(保有技術:</b>                     | ) |

| ( ) IP・サービス        | (保有技術:                            | ) |

| ( )製造•検査           | (保有技術:                            | ) |

| ( )その他( )          | (保有技術:                            | ) |

|                    |                                   |   |

**所在地** 〒153-0051

東京都目黒区上目黒 3-3-14 6F

**電話番号** 03-5723-8123 **FAX 番号** 03-3715-3628

URLhttp://www.tool.co.jp/連絡先営業部sales@tool.co.jp

日本電気株式会社 (NEC) ESS 事業センター

# 事業/製品/サービス/研究内容の概要

LSI/FPGAのC言語設計を世界に先立って実用化し、2001年以来ツールの外販を行っております。また、近年ではC言語からのFPGA/ASICの受託設計や、FPGA/ASIC向けの画像処理C記述販売等も行っております。

# [CyberWokrBench]

ANSI-C、SystemC 記述から、FPGA/ASIC 向けに最適化された RTL(Verilog/VHDL)を合成する高位合成ツールと、Cソース上で、機能及びタイミング(サイクル動作)の検証、デバッグ、形式検証が行える検証ツール群、操作や結果解析用の GUI 等からなる統合設計ツール群です。「All-in-C」コンセプト(制御系もデータ系も C 言語で設計、機能もタイミングも C 言語で検証)を実現する唯一のツールです。

- =CyberWorkBench を導入した効果=

- 1) 設計期間、設計工数の大幅短縮(設計コスト削減) RTL 記述に比べ C 記述は数分の一の記述量で、数百倍の高速検証が可能

- 2) 面積、電力の削減(製造コスト削減)

- 一つの C 記述から様々なアーキテクチャを探索できるため、設計制約にフィットした回路を出すことができ、RTL 設計よりコストの低いチップの設計が可能(特にコンシューマ分野)

- 3) 信頼性向上

- C 言語から直接合成可能なこと、また行数が少なく、検証が高速、検証網羅率が高くしやすい等により信頼度の向上が可能

- 4) H/W 部分の仮想化と組み込みソフトウェアの早期開発(協調検証) 合成可能な C 記述は、組み込みソフト用の仮想環境として利用可能。また、CWB はサイクル精度のモデルも合成 するため、バス混雑度のチェックや割り込み等のタイミングが必要な検証も可能

- 5) アルゴリズム設計者による FPGA 開発

- C・C++記述からの合成が可能なため、H/W の基礎を学べば RTL 無で FPGA が設計可能。RTL 設計者が開発するより効率的な開発が可能

| <b>得意分野</b> ◎最も得意とする分野 | 〇対応可能分野 (保有技術を3つまで記入)                       |   |

|------------------------|---------------------------------------------|---|

| (◎) システム・回路設計/検証       | (保有技術:高位合成、高位検証、ソースデバッガ、形式検証等 )             |   |

| ( ) レイアウト・マスク設計/検      | 証(保有技術:                                     | ) |

| ()パッケージ・ボード設計/検        | 証(保有技術:                                     | ) |

| ( ) デバイス・プロセス設計/検      | 証(保有技術:                                     | ) |

| (O) IP・サービス            | (保有技術:C 言語から RTL への受託設計、画像処理等の C レベルの IP 群) | 1 |

| ( )製造·検査               | (保有技術:                                      | ) |

| ( )その他(                | )(保有技術:                                     | ) |

|                        |                                             |   |

| <b>附在地</b> | 21  | 1-8666 |  |

|------------|-----|--------|--|

|            | ~ ' | 1 0000 |  |

川崎市中原区下沼部 1753 S 棟 24F ESS 事業センター

**電話番号** 044-435-9486 **FAX 番号** 044 -435 - 9491

URL <a href="http://jpn.nec.com/cyberworkbench/">http://jpn.nec.com/cyberworkbench/</a>

連絡先 CWB 問い合わせ窓口 <u>info@cad.jp.nec.com</u>

有限会社 アートグラフィックス

# **EDA Specialist Artgraphics**

|       |     |     | _   |     | _   |

|-------|-----|-----|-----|-----|-----|

| 事業/製品 | /#- | ・ドス | /研究 | 内突( | カ海亜 |

弊社は、Verilog 設計ツールの製品開発と EDA 全般のコンサルテーションを主業務としています。 Verilog 設計ツールは、高性能・低価格の特性を持つと共に、Windows 環境で快適に動作する事が特色です。

# ◆ EDA 製品

- ◇ RTL 論理合成ツール

- ◇ Verilog シミュレータ

- ◇ Verilog HDL から C++への変換ツール

- ◇ Verilog 文書生成ツール

- ◇ Verilog-AMS パーサー

- ◇ SystemVerilog パーサー

| 得意分野    | ◎最も得意とする  | 分野   | 〇対応可能分野      | (保有技術を3つまで記入) |   |

|---------|-----------|------|--------------|---------------|---|

| ()シス    | テム・回路設計/樹 | 証    | (保有技術:       |               | ) |

| ()レイ    | アウト・マスク設  | 計/検証 | (保有技術:       |               | ) |

| ( )パッ   | ケージ・ボード設  | 計/検証 | (保有技術:       |               | ) |

| ()デバ    | イス・プロセス設  | 計/検証 | (保有技術:       |               | ) |

| ( ) IP• | サービス      |      | (保有技術:       |               | ) |

| ( )製造   | • 検査      |      | (保有技術:       |               | ) |

| (◎) その  | 他(RTL     | )    | (保有技術:RTL 論理 | 合成、シミュレーション   | ) |

|         |           |      |              |               |   |

**所在地** 〒124-0012

東京都葛飾区立石 8-14-1

**電話番号** 03-3694-7443 **FAX 番号** 03-3697-9017

URL <a href="http://www.artgraphics.co.jp">http://www.artgraphics.co.jp</a>

株式会社 ジェム・デザイン・テクノロジーズ

# 事業/製品/サービス/研究内容の概要

GemPackage -- LPB 構想設計ツール

(用途) IC パッケージフィージビリティスタディを中心に、チップ IO レベルからボードレベルまで各設計 階層で必要になるプランニング機能を縦に統合した、LSI-Package-Board 構想検討ツールです。ボード側・チップ側両方を考慮してパッケージピン・チップピンのネット割り当てを最適化することができ、電磁界解析ツールにボード形状データとパッケージ形状データを提供し、主要なボード用 CAD/パッケージ用 CAD へ設計データを提供することができます。

(機能) ボードフロアプラン機能、IC パッケージフィージビリティスタディ機能、半導体 RDL 検討機能、チップ IO プラン機能 (New!)、CAD 入出力機能 (Cadence Allegro/APD/SiP, Zuken CR-5000BoardDesigner/CR-8000DesignForce)、シミュレータ接続機能、JEITA LPB フォーマット入出力機能 (C, R, G, N)

GemView/Free -- GPK ビューア(無償)

(用途) GemPackage のデータ (. gpk ファイル) を表示・確認するための無償ビューアです。

(機能)GPK ファイル入出力、2D 表示、3D 表示(Google Earth, SketchUp)、DXF 入力。

GemLPB -- JEITA LPB フォーマット活用促進ツール(参考出品)

(用途) ご利用中の CAD が JEITA LPB フォーマットにまだ対応していなくても、本ツールを利用すれば JEITA LPB フォーマットを入出力することができます。

(機能) GemView/Free の各機能、JEITA LPB フォーマット入出力機能(C, R, G, N)、CAD 入出力機能(Cadence Allegro/APD/SiP, Zuken CR-5000BoardDesigner/CR-8000DesignForce)

| 得意分野    | ◎最も得意とする分野    | 〇対応可能分野      | (保有技術を3つまで記入)                     |   |

|---------|---------------|--------------|-----------------------------------|---|

| ()シス    | .テム・回路設計/検証   | (保有技術:       |                                   | ) |

| ( ) レ1  | アウト・マスク設計/検証  | (保有技術:       |                                   | ) |

| (◎) パッ  | ケージ・ボード設計/検証  | (保有技術:LPB 超階 | 「層設計、スケッチアンドコンバート配線可能性 <b>検</b> 証 | ) |

| ( )デノ   | バイス・プロセス設計/検証 | (保有技術:       |                                   | ) |

| ( ) IP• | サービス          | (保有技術:       |                                   | ) |

| ( )製造   | •検査           | (保有技術:       |                                   | ) |

| ( )その   | 他 ( )         | (保有技術:       |                                   | ) |

|         |               |              |                                   |   |

**所在地** 〒920-1161

石川県金沢市鈴見台 4-8-21

**電話番号** 076-254-5841 **FAX 番号** 076-254-5842

URL <a href="http://www.gemdt.com/">http://www.gemdt.com/</a>

連絡先 代表取締役 村田洋(むらた ひろし)

murata@gemdt.com

株式会社 Trigence Semiconductor

# 事業/製品/サービス/研究内容の概要

Trigence Semiconductor は家電製品、PC、車載プラットフォームで高品質のオーディオを実現するデジタルオーディオ技術を開発し、こうした最先端技術をライセンス供給していま す。独自のデジタル信号処理技術のDnote\* は、デジタル信号を直接スピーカーに送ることによって、消費電力を大幅に削減しつつ音質を格段に改善できます。Trigence は、既存のアナログ・オーディオ・システムが Dnote を使ったデジタル方式に置き換わっていくと期待しています。同社の技術はすでに日本のカー・オーディオ・メーカーにライセンスが供与されており、音質面で も高い評価を得ています。

Trigence Semiconductor の専門分野は、アナログ信号からデジタル信号への変換(AD)とその逆(DA)を行う技術であり、特にミックスドシグナル LSI 回路技術(高精度 AD/DA 変換技術や高速インターフェイス技術など)を得意としています。現在は、電力効率の高いオーディオ機器向けに独自のデジタル信号処理技術であるDnote のライセンスを供給しており、日本の大手カー・オーディオ・システム・メーカーやアミューズメント・マシン・メーカーとライセンス契約を結んでいます。

\*Dnote は、アメリカ合衆国およびその他の国における Trigence Semiconductor の商標です。

| <b>得意分野</b> ◎最も得意とする分野 | 〇対応可能分野 | (保有技術を3つまで記入) |   |

|------------------------|---------|---------------|---|

| (◎) システム・回路設計/検証       | (保有技術:  |               | ) |

| ( ) レイアウト・マスク設計/検証     | (保有技術:  |               | ) |

| ( ) パッケージ・ボード設計/検証     | (保有技術:  |               | ) |

| ( ) デバイス・プロセス設計/検証     | (保有技術:  |               | ) |

| ( ) IP・サービス            | (保有技術:  |               | ) |

| ( )製造·検査               | (保有技術:  |               | ) |

| ( )その他( )              | (保有技術:  |               | ) |

|                        |         |               |   |

**所在地** 〒101-0021

千代田区外神田 4-1 3-5 松源ビル3F

電話番号 03-3525-4434 **FAX 番号** 03-3525-4436

URL <a href="http://www.trigence.co.jp">http://www.trigence.co.jp</a>

**連絡先** <u>sales@trigence.co.jp</u>

日本コントロールシステム株式会社

# 事業/製品/サービス/研究内容の概要

当社は20年以上にわたり、半導体マスク描画装置向けの高速データ変換システムを提供し続けてます。現在はマスクデータ準備のトータルソリューションとして NDE Mask Manufacturable Suite (略称 NDE-MS) というソフトウェアスイートを提供しております。NDE-MS はポスト OPC からマスク描画までをカバーし、検査・測長装置向けデータ準備にも対応したアプリケーション群となっています。

また、当社ではこれまでマスクデータ準備で培った技術をもとに半導体装置内で利用されるソフトウェアの提供 も行っております。

【NDE Mask Manufacturable Suite に含まれるアプリケーション】

・Fracture : 様々な図形演算を含むデータ・フラクチャリングおよび変換

•MRC : マスクルールチェック

•Select : 既存レイヤ群から図形演算に基づくパターン生成

Pattern-Match : テンプレートベースのパターンマッチング

SCRD : Curvilinear/Rectilinear 向けショット削減

PEC : ドーズ変調による近接効果補正

MPC : バイアスによるマスクプロセス補正

EBV : スタンドアロンで軽快なデータビューワ

# 【その他の製品およびサービス】

- ・パターンドメディアテンプレート描画用フォーマッタ

- ・産業用太陽光発電システム設計支援ソフトウェア i-Pals

- ・3 次元画像処理ジェスチャー認識エンジン GREEEN

- ・法人向け携帯認証リモートアクセスシステム SiN-Ku

| 得意分野    | ◎最も得意とする分野   | 〇対応可能分野    | (保有技術を3つまで記入)      |   |

|---------|--------------|------------|--------------------|---|

| ()シス    | テム・回路設計/検証   | (保有技術:     |                    | ) |

| ()レイ    | アウト・マスク設計/検証 | (保有技術:     |                    | ) |

| ( )パッ   | ケージ・ボード設計/検証 | (保有技術:     |                    | ) |

| ( )デバ   | イス・プロセス設計/検証 | (保有技術:     |                    | ) |

| ( ) IP• | サービス         | (保有技術:     |                    | ) |

| (◎)製造   | ∵検査          | (保有技術:分散処理 | 里、フラクチャリング、プロセス補正等 | ) |

| ( )その   | 他( )         | (保有技術:     |                    | ) |

|         |              |            |                    |   |

|         |              |            |                    |   |

**所在地** 〒150-0013

東京都渋谷区恵比寿 1-20-18 三富ビル新館 5 階

**電話番号** 03-3443-5081 **FAX 番号** 03-3443-5189

URL <a href="http://www.nippon-control-system.co.jp/">http://www.nippon-control-system.co.jp/</a>

**連絡先** 新横浜事業所 〒222-0033 横浜市港北区新横浜 2-7-9 TEL∶045-477-5800

濱路 政和 (<u>hamaji@nippon-control-system.co.jp</u>)

プロトタイピング・ジャパン株式会社

# 事業/製品/サービス/研究内容の概要

弊社は 2003 年 10 月に設立された国内におけるプロトタイピングシステムの輸入・開発・販売及び保守を行っております。独創的な最先端 FPGA プロトタイピングテクノロジによって、ASIC 開発 TAT の短縮と開発コストを低減に寄与できることを企業理念としております。関連して周辺部品(ドータボード、ケーブル、コネクタ等)のワンストップ販売を提供して、お客様におけるシステム調達工数およびコストを削減できるお手伝いをさせていただきます。

またプロトタイピングで必要とされる EDA ツールやコンベンショナルな IP 群も取り扱い、FPGA 評価ボードに必要とされるソリューションをまとめて取り扱いをしております。

# 【ASIC プロトタイピングシステム製品例】

- ◇Altera 系 CycloneIVおよび CycloneV 搭載のエコノミータイプ DEO/DE2 シリーズ (台湾 Terasic 社)

- ◇Altera 系 StratixIV および StratixV 搭載のミドルエンド DE4/DE5 シリーズ (台湾 Terasic 社)

- ◇Altera 系 StratixIV を複数チップ搭載した S4Logic/S4Tile シリーズ (米 Polaris 社)

- ◇Xilinx Virtex7 FPGA 搭載のハイエンドモデル(米 S2C 社)

- ◇Xilinx Virtex7 FPGA 搭載のハイエンドモデル(独 PRO DESIGN 社)

# 【ASIC プロトタイピングシステム周辺製品例】

- ◇V by One、DVI、HDMI等、画像処理無向けドータボート(英 Bitec 社)

- ◇コネクタおよびハイスピードケーブル (米 Samtec 社)

# 【EDA ツール】

- ◇FPGA オンチップ計測および RTL デバッグツール(仏 Temento 社 DiaLite シリーズ)

- ◇FPGA 用 HDL デバッガおよび CAD ナビゲーション(蘭 HDL Works 社 HDL Companion シリーズ)

# 【コンベンショナル IP 群】

◇CAN、8051、USB Controller、JPEG エンコーダ/デコーダ、ロイヤリティフリープロセッサ(米 CAST 社)

| 得意分野     | ◎最も得意とする分野   | 〇対応可能   | 6分野    | (保有技術を3        | つまで記入)    |         |   |

|----------|--------------|---------|--------|----------------|-----------|---------|---|

| (◎) シス   | テム・回路設計/検証   | (保有技術:  | FPGA フ | プロトタイピン?       | グ         |         | ) |

| ()レイ     | アウト・マスク設計/検討 | E(保有技術: |        |                |           |         | ) |

| ( ) パッ   | ケージ・ボード設計/検証 | E(保有技術: |        |                |           |         | ) |

| ()デバ     | イス・プロセス設計/検証 | E(保有技術: |        |                |           |         | ) |

| (O) IP • | サービス         | (保有技術:  | 8051、U | SB Controller. | JPEG エンコー | -ダ/デコーダ | ) |

| ( )製造    | •検査          | (保有技術:  |        |                |           |         | ) |

| ( )その    | 他( )         | (保有技術:  |        |                |           |         | ) |

|          |              |         |        |                |           |         |   |

| <b>所在地</b> | T 222-0033 |

|------------|------------|

| 171 E-15   | 1 222 0000 |

横浜市港北区新横浜2-3-4クレシェンドビル7階

**電話番号** 045 - 620 - 0705 **FAX 番号** 045 - 475 - 1313

連絡先 井上 卓也 (<u>inoue@prototyping-japan.com</u>)

スタビリティ株式会社

# 事業/製品/サービス/研究内容の概要

スタビリティ株式会社では、LSI設計及びシステム設計、ソフトウェア開発及びサーバ・ネットワークの管理等々のサービスを提供しています。

2013 年度に新たに EVTools 部門を立ち上げ、ソフトウェア開発における業務効率化を目指した自社製品の開発、販売を行うと共に、ネットワークセキュリティに関わる様々な技術開発、暗号化アルゴリズムの検討・検証等を行っています。

# 販売ツール

**EVTools**

- ◆ CSFAG (Control Structure Flow Automatic Generation tool)

- Cソースコードから制御構造フローグラフを自動生成

- ◆ SCV (Specification with C-source automatic Verification tool)

ソフトウェアユニット背経書とCソースコードを自動検証

- ◆ SAG (Specification Automatic Generation tool)

- Cソースコードからソフトウェアユニット設計書を自動出力

- ◆ CAG (C-source Automatic Generation tool)

ソフトウェアユニット設計書から C ソースコードを自動出力

| 得意分野    | ◎最も得意とする分野   | 〇対応可能分野 | (保有技術を3つまで記入) |  |

|---------|--------------|---------|---------------|--|

| (⊚) シス  | .テム・回路設計/検証  | (保有技術:  | )             |  |

| ()レイ    | アウト・マスク設計/検証 | (保有技術:  | )             |  |

| ( )パツ   | ケージ・ボード設計/検証 | (保有技術:  | )             |  |

| ( ) デバ  | イス・プロセス設計/検証 | (保有技術:  | )             |  |

| (O) IP• | サービス         | (保有技術:  | )             |  |

| ( )製造   | •検査          | (保有技術:  | )             |  |

| ()その    | 他( )         | (保有技術:  | )             |  |

|         |              |         |               |  |

| 所在地         | 〒220−8120  |

|-------------|------------|

| 171 TLL MIS | 1 220 0120 |

神奈川県横浜市西区みなとみらい ランドマークタワー20F

**電話番号** 0120-725-710 **FAX 番号** 0120-724-701

URL <a href="http://stability.jp">http://stability.jp</a>

連絡先 ※ ev-sales@stability.jp

株式会社アプリスター

# 事業/製品/サービス/研究内容の概要

アプリスターは2001年5月に創業し、主に設計支援ツールの開発販売、受託設計、教育コンサルティング事業を中心に事業を行って参りました。得意とする分野は上位設計支援ツールやモデリングです。2008年にベトナム ハノイに子会社 Applistar Vietnam を設立し、オフショアでの受託設計サービスを展開しています。

◆車載制御ソフトウェアのエレ・メカ協調検証ツール

SystemC によるデジタル、アナログ、メカモデルの記述と高速エミュレータによる協調検証が可能です。

# ◆ FPGA プロトタイプボード

弊社が取り扱っております Dini 社製プロトタイピングボードは、Xilinx Virtex7/ Kintex7 ならびに Altera Stratix5 などの FPGA を搭載した製品ラインアップを充実いたしました。

- ◇Xilinx Virtex7 搭載プロトタイピングボード

- -7V2000T 4 個搭載 56M ゲートプロトタイピングボード DNV7F4A(2 枚スタック使うことも可能です!)

- ・7V2000T 2 個搭載 28M ゲートプロトタイピングボード DNV7F2A(2 枚スタック使うことも可能です!)

- •7V2000T 1 個搭載 14M ゲートプロトタイピングボード DNV7F1A

- ◇Altera Stratix5 搭載プロトタイピングボード

- -5SGXAB 2 個搭載 16.5M ゲートプロトタイピングボード DNS5GX F2

- ◇Xilinx Kintex7 搭載プロトタイピングボード

- •Kintex 7 1 個搭載 高速パケット処理用 FPGA ボード DNPCle\_10G\_K7\_LL

- •Kintex 7 1 個搭載 高速パケット処理用 FPGA ボード DNPCle\_10G\_K7\_LL\_QSPF

# ◆ 受託設計サービス

弊社は、ベトナムに子会社を設立し、受託設計サービスを低コストでお受けしております。

- ・SOC/FPGA 仕様からの SystemC/HDL 設計、PCB 設計、・ハード/ソフト協調検証環境構築、組込み系ソフトウェア の開発解析に至るさまざまな工程でご活用いただけます。

- ◆ 高速 Verilog/Matlab 協調シミュレーション環境 FinSimMath

Fintronic USA 社の FinSimMath の取り扱いをしています

|                    | 「る分野に◎ (1 つまで)、対応可能分野に〇 (複数可) をご記入下さい。 |   |

|--------------------|----------------------------------------|---|

| ※保有技術を3つまで記入して下さい  |                                        |   |

| (◎)システム・回路設計/検証    | (保有技術:SystemC コンパイラ、高速協調検証ツール構築技術      | ) |

| ( ) レイアウト・マスク設計/検証 | (保有技術:                                 | ) |

| (○) パッケージ・ボード設計/検証 | (保有技術:PCB 設計サービス                       | ) |

| ( ) デバイス・プロセス設計/検証 | (保有技術:                                 | ) |

| (O) IP・サービス        | (保有技術:オフショア組み込みシステム開発 サービス             | ) |

| ( )製造·検査           | (保有技術:                                 | ) |

| ( )その他( )          | (保有技術:                                 | ) |

|                    |                                        |   |

**所在地** 〒243-0018

神奈川県厚木市中町3-9-10 中町武井ビル3階

**電話番号** <u>046-248-7749</u> **FAX 番号** <u>046-248-7759</u>

URL <a href="http://www.applistar.com">http://www.applistar.com</a>

連絡先 営業部 support@applistar.com

株式会社 ESL 研究所

# 事業/製品/サービス/研究内容の概要

# ビジョン

株式会社 ESL 研究所は国産 EDA 開発の「魂」を抱く有志により設立されました。

今後我が国で加速化する高齢化社会に対応した様々な社会システム及びそれを支える"制御機械"が要求される。並列・分散コンピューティングやクラウドコンピューティングによる無事故自動運転自動車、介護用自立ロボット等々、必要となる制御機械は多数あるが、それを効率良く設計する手段が未確立である。

当社はその要求に応え、クラウドコンピューティングや並列・分散コンピューティングを用いた実時間・複合シミュレーション技術の確立によるハイパー設計・検証環境を実現し、将来の全国民の幸福につながる社会を目指すものとする。

# 開発プロジェクト

1) 車載組込みシステムの安全性・信頼性を向上するハイブリッド検証プラットフォームの開発

メカ・アナログ回路をソフトウェア等のデジタル系回路と検証可能とするハイブリッドモデルを開発し、FPGA上での検証時間の短縮化を図るテスト環境の開発

2) 高速協調検証のための車載用ハイブリッドモデルの開発

FPGA 上で高速実行なプログラミング言語を用いて記述したソフトウェア、ハードウェア、アナログ回路の「ハイブリッド検証モデル」の開発

3) GP-GPU を利用した大規模高速並列論理シミュレーション装置の開発

「汎用デスクトップパソコン+GPUボーード」を使用した大規模高速並列論理シミュレーション環境の開発

4) FPGA を利用した高速ハードウェア論理シミュレーションエンジンの実用化開発

高速な論理シミュレーションのハードウェアアルゴリズムを FPGA に実装したハードウェアシミュレータシステムの開発

|         |               |         |               | _ |

|---------|---------------|---------|---------------|---|

| 得意分野    | ◎最も得意とする分野    | 〇対応可能分野 | (保有技術を3つまで記入) |   |

| (◎) シス  | 、テム・回路設計/検証   | (保有技術:  | )             |   |

| ()レイ    | アウト・マスク設計/検証  | (保有技術:  | )             |   |

| ( ) パッ  | ケージ・ボード設計/検証  | (保有技術:  | )             |   |

| ()デバ    | バイス・プロセス設計/検証 | (保有技術:  | )             |   |

| ( ) IP• | サービス          | (保有技術:  | )             |   |

| ( )製造   | • 検査          | (保有技術:  | )             |   |

| ( )その   | 他( )          | (保有技術:  | )             |   |

|         |               |         |               |   |

|         |               |         |               |   |

| 所在地  | <b>〒</b> 277-0074                    |                       |

|------|--------------------------------------|-----------------------|

|      | 千葉県柏市今谷上町21-3                        |                       |

| 電話番号 | <u>090 −5305 −5497</u> <b>FAX 番号</b> | <u>04-7175 - 4539</u> |

| URL  | http://                              |                       |

| 連絡先  | 代表取締役 染谷 勤                           |                       |

|      | someya@esl-laboratory.com            |                       |

|      |                                      |                       |

株式会社アナジックス

# 事業/製品/サービス/研究内容の概要

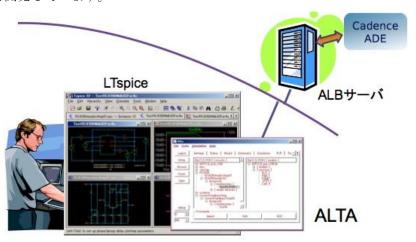

高度な知識と経験を要する専門家が、型にはまった退屈な仕事から解放され、より知的な活動に専念でき、さらに次世代に知識を継承できるよう、情報処理技術を活用し専門家の業務遂行を支援することを目的に 2009 年 1 月に創業しました。Anagix という社名は、アナログ (Analog)設計など匠の仕事を、迅速 (Agile)に支援するために、Unix に象徴されるソフトウェアを活用するということからつけました。

半導体回路設計の CAD ソフト ALB・ALTA を開発販売しています。

ALB・ALTA は Web ブラウザから使うことのできる半導体集積回路用の回路解析・設計システムであり、再利用と流通に適した設計資料の作成を容易にします。Web サーバである ALB(Anagix Library Builder)とローカルコンピュータ上の ALTA (Anagix Local Tools Assistant)プログラムの連携により、PC 上のパーソナル設計ツール (LTspice) および業界標準の Cadence 社の Virtuoso を用いて作成した設計データを相互に変換できます。

弊社では、フリーソフトやオープンソースソフトを積極的に活用し、EDA のローコスト化を目指します。専門家のアナログ設計を支援する一方、オープン化により半導体設計の民主化を追求します。開発には主に日本発の Ruby 言語を使い、少数精鋭で開発しています。

| <b>得意分野</b> ◎最も得意とする分野 | ○対応可能分野 (保有技術を 3 つまで記入)               |   |

|------------------------|---------------------------------------|---|

| (◎) システム・回路設計/検証       | (保有技術:Web ベースの回路設計環境、SPICE シミュレーション技術 | ) |

| ( ) レイアウト・マスク設計/検証     | (保有技術:                                | ) |

| ()パッケージ・ボード設計/検証       | (保有技術:                                | ) |

| ( ) デバイス・プロセス設計/検証     | (保有技術:                                | ) |

| (O) IP・サービス            | (保有技術:アナログ回路設計コンサルティング/サポート           | ) |

| ( )製造·検査               | (保有技術:                                | ) |

| (O) その他 ( )            | (保有技術:設計環境(EDA環境)構築サービス               | ) |

|                        |                                       |   |

所在地 〒249-0004

神奈川県逗子市沼間3-22-27

**電話番号** 046-873-3610 **FAX 番号** - -

URL <a href="http://www.anagix.com">http://www.anagix.com</a>

連絡先 代表取締役 森山 誠二郎 Email: seijiro.moriyama@anagix.com

# 【賛助会員】

株式会社 半導体理工学研究センター

# 事業/製品/サービス/研究内容の概要

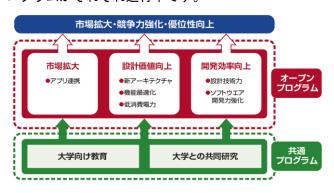

1995年に半導体設計技術力強化を目的とし、日本の主要半導体メーカの出資で設立された民間のコンソーシアムです。当初から国内大学の半導体関連研究基盤拡大のための「大学との共同研究」、「半導体設計技術教育」の両プログラムを中心に活動して来ています。また、2001年からは、上記活動に加え、半導体の微細化に伴う設計の困難さを解決する「設計基盤技術開発」プログラムをクライアント企業と共同で実施して来ました。

一方で、特にここ数年間の半導体産業をとりまく環境と状況の変化に対応すべく、2011 年度より、「半導体市場規模の拡大」、「設計価値向上」、「開発効率向上」を三本柱とした設計力強化のための複数のプログラムを開始しました。これらのプログラムの対象領域は、ソフトウェアも含む設計関連技術開発、実証のための製品設計、集積回路に搭載される IP 設計と検証、ソフト開発および新アプリケーション開拓まで含む広がりを有しています。

大学との共同研究では、1年間の研究(IS:Idea Scout)と通常3年間に亘る研究(FS:Feasibility Study)の 2つのプログラムが合計で約50件通年で運営されています。また、50超の大学に対し年間約2300人の学生に対して SoC 設計教育講座を提供しています。クライアント企業間の共同研究・開発としては、現在は「アプリ分野との連携」、「新 TCAD プラットフォーム開発」、「EDA ツール共同評価」、「 $\beta$  変換 ADC 実用化研究」、「IP コア流通支援」、「HiSIM ユーザ連絡会」の各プログラムがそれぞれ進行中です。

| 得意分野 ◎最も得意とする分野   | 野 〇対応可能分野        | (保有技術を3つまで記入) |   |

|-------------------|------------------|---------------|---|

| (〇) システム・回路設計/検証  | (保有技術:           |               | ) |

| ( ) レイアウト・マスク設計/材 | <b>倹証(保有技術</b> : |               | ) |

| ( ) パッケージ・ボード設計/村 | <b>倹証(保有技術</b> : |               | ) |

| (O) デバイス・プロセス設計/标 | <b>倹証(保有技術</b> : |               | ) |

| ( ) IP・サービス       | (保有技術:           |               | ) |

| ( )製造·検査          | (保有技術:           |               | ) |

| (◎)その他(大学との共同研究   | )(保有技術:          |               | ) |

|                   |                  |               |   |

|                   |                  |               |   |

**所在地** 〒222-0033

神奈川県横浜市港北区新横浜3丁目17番地2友泉新横浜ビル6階

**電話番号** 045-478-3300 **FAX 番号** 045-478-3310

連絡先 企画管理部 樋渡 有

# 【賛助会員】

株式会社図研

# 事業/製品/サービス/研究内容の概要

●エレクトロニクス設計ソリューション (EDA事業)

図研は、1976年の設立以来エレクトロニクス実装設計のためのソフトウェア製品において常に最先端の技術を提供してまいりました。日本で生まれ、お客様の厳しい品質要求を満たすことで培われてきた図研のエレクトロニクス設計ソリューションは、難易度の高い設計課題にチャレンジし続けなければならない世界中のハイテク企業において多数採用されています。

- ・エンジニアリング PLM ソリューション (DS-2) ・構想設計ソリューション (System Planner)

- ・プリント基板設計/IC パッケージ設計/LSI との協調設計ソリューション(Design Force)

- ・FPGA 設計環境との連携ソリューション(GPM)・製造設計ソリューション(DFM Center)

# ●モノづくり基盤ソリューション(プリサイト事業)

図研は、エレクトロニクス設計分野にとどまらず、企業全体の製品開発・製造プロセスの高度化、効率化に取り組んでいます。設計、製造、調達、サービスなど、エンジニアリングチェーンやサプライチェーン全体を最適化する IT ソリューションやサービスを提供していくために事業領域を拡張しています。

- ・統合 BOM エンタープライズ PLM(PreSight) ・ナレッジ活用ソリューション(Knowledge Explorer)

- ・3D CAD ソリューション(CATIA V5)

- ・3D データ活用ソリューション(XVL series)

# ●オートモーティブ&マシナリー設計ソリューション

ワイヤハーネス設計ソリューションを中心に世界の主要オートモーティブサプライアに設計環境を提供してきた図研は、 今後も最先端のオートモーティブ設計ソリューションを開発・提供しつづけていくためその事業を強化します。日本ととも に自動車開発の先進国であるドイツの開発拠点との連携によりグローバルな開発体制を構築し、先進のオートモーティ ブ設計のための技術開発を推進してまいります。

・ワイヤハーネス設計ソリューション(Cabling Designer) ・ケーブル設計ソリューション(E3. series)

| 得意分野    | ◎最も得意とする分野   | 〇対応可能分野 (保有技術を3つまで記入)                                |   |

|---------|--------------|------------------------------------------------------|---|

| (〇) シス  | テム・回路設計/検証   | (保有技術:システム全体構想設計、システム全体回路設計                          | ) |

| (0) レイ  | アウト・マスク設計/検証 | $\mathbb{R}$ (保有技術: $\mathbb{R}/0$ プランニング、自動配線、コデザイン | ) |

| (◎) パッ  | ケージ・ボード設計/検証 | (保有技術:自動配線、同時並行設計、FPGA 設計、各種解析                       | ) |

| ( )デバ   | イス・プロセス設計/検証 | (保有技術:                                               | ) |

| ( ) IP• | サービス         | (保有技術:                                               | ) |

| (〇) 製造  | •検査          | (保有技術 : パネル設計、自動補正、アートワーク編集                          | ) |

| ( )その   | 他( )         | (保有技術:                                               | ) |

|         |              |                                                      |   |

**所在地** 〒224-8585

横浜市都筑区荏田東 2-25-1

**電話番号** 045-942-1711 **FAX 番号** 045-942-1712

URL <a href="http://www.zuken.co.jp">http://www.zuken.co.jp</a>

**連絡先** EDA 事業部 EL 開発部 ELN セクション

古賀一成(コガカズナリ)<u>koga@zuken. co. jp</u>

渡邊 孝博(わたなべたかひろ)・早稲田大学大学院情報生産システム研究科・教授

# 事業/製品/サービス/研究内容の概要

LSI および PCB の設計効率と設計品質の向上を目指して、システムのアーキテクチャ、EDA 技術、高性能・低消費電力化技法、および、応用の研究開発を行っています。

# 【キーワード】

ネットワークオンチップ(NoC)、プロセッサ、キャッシュ、低電力設計、RDL 配線、等長配線

# 【最近の主な論文/記事/展示等の公開物】

- •X. Jiang, L. Zeng, T. Watanabe: "A Sophisticated Routing Algorithm in 3D NoC with Fixed TSVs for Low Energy and Latency," IPSJ Trand.SLDM, 2014(to appear)

- ・ 亀井,渡邊,川北: "LVS の出力情報を活用した VLSI 電源配線幅の高速検証システム,"信学論. J96-D 5, 2013 年 5 月

- •X. Jiang, R. Zhang, T. Watanabe: "An Efficient Algorithm for 3D NoC Architecture Optimization," IPSJ Trans.SLDM, 6, 34–41, Feb. 2013

- •C. Li, Y. Dong, T. Watanabe: "Region Oriented Routing FPGA Architecture for Dynamic Power Gating," IEICE Trans. Fudamentals,E95-A. Dec.2012

- Y. Dong, C.Li, Z.Lin, H.Zhang, T. Watanabe: "High Performance Feedforward Neural Network Mapped by NoC Architecture with a New Routing Strategy Implementation Method," J. Signal Processing, vol.15, No.3, pp.113-122, Mar. 2011

- •J. Ye, Y. Wan, T. Watanabe: "A New Recovery Mechanism in Superscalar Microprocessors by Recovering Critical Misprediction," IEICE Trans.Fund. Electoronics, Comm. Computer Sciences, E94-A/12,2639-2648, Dec. 2011

| 得意分野    | ◎最も得意とする分野           | 〇対応可能分野 (保有技術を3つまで記入)              |   |

|---------|----------------------|------------------------------------|---|

| (O) シス  | テム・回路設計/検証           | (保有技術:低電力キャッシュ構成、NoC 構成技術          | ) |

| (◎) レイ  | アウト・マスク設計/検証         | (保有技術:LSI/PCB 自動配置・配線、レイアウト検証、寄生抽出 | ) |

| (0) パッ  | ケージ・ボード設計/検証         | (保有技術:フリップチップの RDL 配線アルゴリズム        | ) |

| ( )デバ   | イス・プロセス設計/検証         | (保有技術:                             | ) |

| ( ) IP• | サービス                 | (保有技術:                             | ) |

| ( )製造   | <ul><li>検査</li></ul> | (保有技術:                             | ) |

| ( )その   | 他 ( )                | (保有技術:                             | ) |

|         |                      |                                    |   |

| <b>所</b> 在地 | <b>⊤</b> 808−0135 |

|-------------|-------------------|

| <b>川住地</b>  | T 808-0135        |

北九州市若松区ひびきの 2-7

**電話番号** 093-692-5371 **FAX 番号** 093-692-5371

URLhttp:// www.f. waseda. jp/watt/連絡先渡邊孝博watt@waseda. jp

井上 靖秋(いのうえやすあき)・早稲田大学大学院情報生産システム研究科・教授

# 事業/製品/サービス/研究内容の概要

ミクストシグナル LSI の設計・検証技術設の研究、特に、定電圧低電力高効率を目指したミクストシグナル LSI 設計技術、回路シミュレーション、モデリング、タイミング検証等の設計検証技術の研究開発を行っています。

# 【キーワード】

ミクストシグナルLSI、CAD、回路シミュレーション、タイミング解析、非線形回路、数値解析

# 【最近の主な論文/記事/展示等の公開物】

- \* Zhou JIN, Xiao WU, Dan NIU, and Yasuaki INOUE, "Effective implementation and embedding algorithms of CEPTA method for finding DC operating points," IEICE Trans. Fund., vol. E96-A, no.12, pp. 2524-2532, Dec. 2013.

- \* Dan Niu, Kazutoshi Sako, Guangming Hu and Yasuaki Inoue, "A globally convergent nonlinear homotopy method for MOS transistor circuits," IEICE Trans. Fund., vol. E95-A, no.12, pp.2251-2260, Dec. 2012.

- \* Yasuaki Inoue, Changquan Jin, Zhao Chen and Zhangcai Huang, "An almost 2VDD rail-to-rail input and output operational amplifier using VDD CMOSFETs," Proc. IEEJ 2011 International Analog VLSI Workshop, pp.5-8, November 2011.

- \* Zhangcai Huang, Atsushi Kurokawa, Masanori Hashimoto, Takashi Sato, Minglu Jiang, and Yasuaki Inoue, "Modeling the overshooting effect for CMOS inverter delay analysis in nanometer technologies," IEEE Trans. CAD, vol.29, no.2, pp. 250–260, February 2010.

- \* Ryosuke Inagaki, Norio Sadachika, Dondee Navarro, Mitiko Miura-Mattausch, and Yasuaki Inoue, "A GIDL-current model for advanced MOSFET technologies without binning," IPSJ Trans. SLDM, vol.2, pp.93-102, February 2009.

- \* Shin-ichi Ohkawa, Hiroo Masuda, and Yasuaki Inoue, "A novel expression of spatial correlation by a random curved surface model and its application to LSI design," IEICE Trans. Fund., vol.E91-A, no.4, pp.1062-1070, April 2008.

| 得意分野    | ◎最も得意とする分野   | 〇対応可能分野 (保有技術を3つまで記入)         |   |

|---------|--------------|-------------------------------|---|

| (⊚) シス  | .テム・回路設計/検証  | (保有技術:回路シミュレーション技術,アナログ要素回路技術 | ) |

| ()レイ    | アウト・マスク設計/検討 | E(保有技術:                       | ) |

| ( )パッ   | ケージ・ボード設計/検証 | (保有技術:                        | ) |

| ( )デバ   | イス・プロセス設計/検討 | E(保有技術:                       | ) |

| ( ) IP• | サービス         | (保有技術:                        | ) |

| ( )製造   | •検査          | (保有技術:                        | ) |

| ()その    | 他(           | (保有技術:                        | ) |

|         |              |                               |   |

|         |              |                               |   |

| <b>⊤</b> 808-0135 |

|-------------------|

|                   |

|                   |

北九州市若松区ひびきの 2-7

電話番号 093-692-5372 FAX 番号 093-692-5372

URL <a href="http://www.f.waseda.jp/inoue\_yasuaki/">http://www.f.waseda.jp/inoue\_yasuaki/</a></a>

連絡先

井上靖秋

inoue\_yasuaki@waseda.jp

築山 修治 (つきやま しゅうじ)・中央大学 理工学部 電気電子情報通信工学科・教授

# 事業/製品/サービス/研究内容の概要

アルゴリズム開発に興味を持ち、ディジタル回路設計技術の高性能化・高効率化、ならびに小型液晶ディスプレイ用駆動回路の回路設計手法の研究などを行っています。

#### 【キーワード】

統計的設計手法,静的遅延解析,最適配線手法,液晶駆動回路設計,NMOS 単チャネル回路

# 【最近の主な論文/記事/展示等の公開物】

- ・ 水津 太一, 築山 修治, "小型 SoG-LCD の入力信号配線に対する最適設計手法とその評価", 信学論 A, vol.J97-A, no.7, pp.519-527, 2014.

- Shuji Tsukiyama, Masahiro Fukui, "A new delay distribution model with a half triangular distribution for statistical static timing analysis," IEICE Trans. Fundamentals, vol.E96-A, no.12, pp.2542-2552, 2013.

- Shuji Tsukiyama, Masahiro Fukui, "A statistical maximum algorithm for Gaussian mixture models considering the cumulative function curve," IEICE Trans. Fundamentals, vol.E94-A, no.12, pp.2528-2536, 2011.

- Shingo Takahashi, Shuji Tsukiyama, Masanori Hashimoto, Isao Shirakawa, "A sampling switch design procedure for active matrix liquid crystal displays," IEICE Trans. Fundamentals, vol.E89-A, no.12, pp.3538-3545, 2006.

- 比嘉晋士,栗田知拓,築山修治, "小型液晶ディスプレイ駆動回路用 nMOS ダイナミックシフトレジスタとその評価", 信学技報 VLD2013-137, 2014.

- ・ 佐々木大介, 築山修治, 松永真理子, 高橋真吾, "直列接続された組電池の統計的寿命解析手法について", 信学技報 VLD2013-138, 2014.

- ・ 築山修治,神戸尚志,福井正博,ビジュアルに学ぶディジタル回路設計,コロナ社,2010.

| <b>得意分野</b> ◎最も得意とする分野 | 〇対応可能分野 (保有技術を3つまで記入)             |   |

|------------------------|-----------------------------------|---|

| (○) システム・回路設計/検証       | (保有技術: NMOS 単チャネル回路               | ) |

| (◎)レイアウト・マスク設計/検証      | E(保有技術: 統計的静的遅延解析手法,最適配線手法,GP-GPU | ) |

| ( ) パッケージ・ボード設計/検討     | E(保有技術:                           | ) |

| ( ) デバイス・プロセス設計/検証     | : (保有技術:                          | ) |

| ( ) IP・サービス            | (保有技術:                            | ) |

| ( )製造·検査               | (保有技術:                            | ) |

| (〇) その他 (              | (保有技術: 組電池の寿命解析手法                 | ) |

|                        |                                   |   |

| 所在地     | 〒112-8551  |

|---------|------------|

| // IL-6 | 1 112 0001 |

東京都文京区春日 1-13-27

**電話番号** <u>03-3817-1871</u> **FAX 番号** <u>03-3817-1847</u>

URL

http://www.elect.chuo-u.ac.jp/tsuki/

連絡先

築山修治

tsuki@elect.chuo-u.ac.jp

永田 真(ながたまこと)・神戸大学大学院システム情報学研究科・教授

# 事業/製品/サービス/研究内容の概要

VLSI システムのノイズ問題全般について幅広く研究開発を進めています。具体的には、

- ① VLSI チップ内の回路動作による電源ノイズ発生、チップ・パッケージ・ボード統合系におけるノイズ伝搬、チップ内の回路間におけるシリコン基板を経由したノイズ結合と干渉など、VLSI チップの設計工程において 考慮すべきノイズ事象の解明と対策およびシミュレーション方法の追求

- ② VLSI チップのノイズが深く関与するエレクトロニクス機器の外部指標への対応、例えば、電磁環境両立性 (EMC):ノイズ発生とノイズ耐性に関する国際標準とチップ開発の整合、ハードウェアセキュリティ:ノイズを伝わる情報漏えいやノイズを使ったサイバー攻撃の理解と対策、他

- ③ VLSI チップのノイズを低減する新材料や新構造の導入など、先端実装技術の探索とノイズを意識した設計へのフィードバック

等をトピックに、先進性と実応用をモットーとして国内外の企業様と連携した研究活動を展開しております。

【キーワード】VLSI システムのノイズ、オンチップノイズモニタ、シグナル・パワーインテグリティ、基板クロストーク、電磁環境両立性(EMC)、サイドチャネル情報漏洩、先端実装、三次元積層と TSV、ノイズ吸収材料、等。

# 【最新の研究成果】

- [1] "Chip Level Simulation of Substrate Noise Coupling and Interference in RF ICs with CMOS Digital Noise Emulator," IEICE Trans. Electronics, Vol. E97-C, No. 6, pp. 546-556, June 2014. 【上記分野①】

- [2] "AC Power Supply Noise Simulation of CMOS Microprocessor with LSI Chip-Package-Board Integrated Model," IEICE Trans. Electronics, Vol. E97-C, No. 4, pp. 264-271, Apr. 2014. 【上記分野①】

- [3] "Power Noise Measurements of Cryptographic VLSI Circuits Regarding Side-Channel Information Leakage," IEICE Trans. Electronics, Vol. E97-C, No. 4, pp. 272-279, Apr. 2014. 【上記分野②】

- [4] "Measurements and Analysis of Substrate Noise Coupling in TSV based 3D Integrated Circuits," IEEE Trans. Components, Packaging and Manufacturing Technology, Vol. 4, No. 6, pp. 1026-1037, June 2014. 【上記分野③】

| <b>得意分野</b> ◎最も得意とする分野 | 〇対応可能分野    | (保有技術を3つまで記入)             |

|------------------------|------------|---------------------------|

| (◎) システム・回路設計/検証       | (保有技術:電源ノイ | ズ・基板ノイズシミュレーション、チップ評価・解析) |

| ( ) レイアウト・マスク設計/検証     | (保有技術:     | )                         |

| (O) パッケージ・ボード設計/検証     | (保有技術:チップ・ | パッケージ・ボード協調シミュレーション・統合設計) |

| ()デバイス・プロセス設計/検証       | (保有技術:     | )                         |

| (O) IP・サービス            | (保有技術:オンチッ | プモニタ )                    |

| ( )製造·検査               | (保有技術:     | )                         |

| ( )その他( )              | (保有技術:     | )                         |

|                        |            |                           |

| 所在地 | <b>〒</b> 657−850 <sup>-1</sup> |

|-----|--------------------------------|

| 刀工地 | 1 007 000                      |

神戸市灘区六甲台町 1-1

電話番号

078-803-6569

FAX 番号

078-803-6221

URL

http://www.cs26.scitec.kobe-u.ac.jp/farm/LSI/

連絡先 永田 草

nagata@cs.kobe-u.ac.jp

村岡 道明(むらおかみちあき)・高知大学理学部・教授 工学博士

# 事業/製品/サービス/研究内容の概要

システムやLSIの設計自動化を目指した技術の研究開発を行っています。研究分野としては、システム・アーキテクチャ設計や機能・論理設計の設計自動化技術、および、GPUやマルチコアプロセッサを用いた並列処理によるEDAアルゴリズムの高速化などを進めています。また、医療情報に関する分散データベースや医療データ解析技術についても研究を進めています。

# 【最近の主な研究内容や主要論文/研究発表】

# <システム・アーキテクチャ設計技術の研究>

システムや LSI のシステム・アーキテクチャ設計に関する EDA 技術の研究開発を進めています。

- ・システムやアーキテクチャ設計(高位設計)の自動化技術(DA)の研究開発として、通産省/NEDO 委託プロジェクト(プロジェクト名:「システムオンチップ先端設計技術の研究開発」)を推進しました。期間: 2000 年 4 月~2004 年 3 月。

- ・最近は、車載電子制御システムの EDA として必要とされる大規模システム検証技術やメカ/アナログ/デジタル/ソフトウェアのハイブリッド検証技術の研究開発を手がけています。

# <機能・論理設計の EDA 技術の研究>

・並列処理技術による高速検証の実現

GPU やマルチコアプロセッサを用いた並列処理による機能・論理検証の高速化技術の研究開発を進めており、車載電子制御システムなどの大規模システムの検証の高速化を目指しています。

・動的クロストーク解析技術

システムや LSI のクロストークを動的に効率よく解析・検証を可能とする技術の研究を行ってきました。

# <医療情報技術の研究>

・医療用分散データベース

複数の病院間(異種のデータベース間)で医療データの交換を可能とする分散データデースの研究を進めてきました。

・医療データ解析の研究

医療用 DWH(データベース)内の診療データや検査データを用いたデータ解析の研究を行ってきました。例として、投薬とその効果を関係を調べるためのデータ解析の研究なども進めてきました。

| 得意分野 ◎最も得           | 意とする分野 (   | )対応可能分野 (1     | <b>呆有技術を3つまで記入</b> ) |             |   |

|---------------------|------------|----------------|----------------------|-------------|---|

| (◎)システム・回路          | 各設計/検証 (伊  | ¦有技術:システム・     | アーキテクチャ生成技術          |             | ) |

| (O) レイアウト・マ         | マスク設計/検証(例 | ·有技術:クロストー     | ク解析                  |             | ) |

| (O) パッケージ・ <b>オ</b> | ボード設計/検証(例 | ₹有技術:FPGA向     | アルゴリズム               |             | ) |

| ( ) デバイス・プロ         | コセス設計/検証(例 | ·有技術:          |                      |             | ) |

| (O) IP・サービス         | (1         | 段有技術:          |                      |             | ) |

| ( )製造·検査            | (1         | R有技術:          |                      |             | ) |

| (〇) その他(            | ) (1       | 呆有技術:GPU やマルチニ | ア による並列アルゴリズ         | ムを用いた高速処理技術 | ) |

|                     |            |                |                      |             |   |

|                     |            |                |                      |             |   |

| 所在地 | 〒780−8520 |

|-----|-----------|

|     |           |

高知市曙町 2-5-1 高知大学 理学部 情報科学コース

電話番号

088-844-8332

FAX 番号

同左

URL

http://www.is.kochi-u.ac.jp/~muraoka/

連絡先 <u>muraoka@is.kochi-u.ac.jp</u>

# 「日本 EDA ベンチャー連絡会」設立趣意

私たちは、日本の EDA の発展を目的として、最新技術情報の交換および共有、技術者間の人的交流および連携の模索、ベンチャー支援等に関わることを企画し、2006 年 1 月、日本 EDA ベンチャー連絡会(略称: JEVeC)を設立いたします。

日本の電子工業は、セットメーカー、電子部品メーカー、材料メーカー、装置メーカー、デザインハウスから構成され、いずれもその技術や製品においてグローバルな競争力を有し、これらの総合力が日本の力の源泉の一つとなっております。その中において、これらの製品開発の重要要素である製品企画および設計において、競争力に直結する不可欠の役割を担う EDA は、その多くを米国製品に依存し、日本の EDA は産業として電子工業の中で相対的に弱小な存在であります。

また、電子デバイスの機能規模拡大に伴う検証や、ソフトウエア協調設計における諸難題、低消費電力とハイスピード双方への高い要求、微細化の進展と歩留まり向上、開発期間の短縮等、開発者の抱える課題は増大する一方であります。こうした課題は EDA と歩調を合わせて実際的に解決していくことが極めて有効であるものの、残念ながら現在はこうした EDA が日本国内にバランスよく育っていないのが実状となっております。

他方、電子デバイス業界の内部で活躍していた優秀な EDA 技術者や大学の先生方が多数 EDA ベンチャーを創業するなど、新しい流れも生まれつつあり、技術内容も上流設計から DFM まで大きく広がっております。米国大手企業の寡占の中で、個別技術要素に強い日本の EDA が成長していくためには、この流れを更に大きなものにしていくことが望まれますが、幸い、国レベルでは半導体業界を始めとして、電子工業全体の発展のために様々な施策が打たれております。EDA もこうした施策の輪の中に積極的に参入し、日本の電子工業のピラミッドの中に定位置を占めるべく、その実力を大きく高めていく必要があります。

その実現のため、日本で EDA 開発に携わっている私たちが、お互いを知り合い、切磋琢磨し、互いの強みを活かした連携を模索し、単独では成し難い成長を目指して知恵を絞り合い協力する場として、本会を設立いたします。本会では、下記の活動を通し、日本において EDA 開発を行っているベンチャー企業・

部門会員相互の交流だけではなく、官公庁や大学、あるいは海外の EDA 関連研究機関、さらには顧客内部の EDA 関連技術者やユーザーとも交流を深め、日本電子工業全体の発展に大きく貢献することを目指します。

# 【主な活動予定内容】

- 1. 企業や大学研究機関における EDA 関連情報の整備およびネットワーク作り

- 2. EDA 関連事業の起業支援

- 3. 共同開発、共同受託、事業協力、技術提携の支援

- 4. 特許等知的所有権の相互利用の斡旋

- 5. 産学連携の強化:共同研究開発、新卒採用協力

- 6. 行政との情報交換窓口

- 7. 会報発行

2006 年 1 月 23 日 日本 EDA ベンチャー連絡会

# 会員名簿(2014年9月現在)

| 【正会員】                       | URL                                    |

|-----------------------------|----------------------------------------|

| 株式会社アストロン                   | http://www.astron.co.jp/               |

| 株式会社 日立ハイテクサイエンス            | http://www.hitachi-hitec-science.com/  |

| ケイレックス・テクノロジー株式会社           | http://www.keirex.com/                 |

| 株式会社ジーダット                   | http://www.jedat.co.jp/                |

| 株式会社 NTT データ数理システム          | http://www.msi.co.jp/                  |

| 株式会社東京システム技研                | http://www.tsl.co.jp/                  |

| TOOL 株式会社                   | http://www.tool.co.jp/                 |

| 日本電気株式会社                    | http://www.cyberworkbench.com/         |

| 有限会社アートグラフィックス              | http://www.artgraphics.co.jp/          |

| 株式会社ジェム・デザイン・テクノロジーズ        | http://www.gemdt.com/                  |

| 株式会社 Trigence Semiconductor | http://www.trigence.co.jp/             |

| 日本コントロールシステム株式会社            | http://www.nippon-control-system.co.jp |

| プロトタイピング・ジャパン株式会社           | http://prototyping-japan.com/          |

| スタビリティ株式会社                  | http://stability.jp/                   |

| 株式会社アプリスター                  | http://www.applistar.com/              |

| 株式会社 ESL 研究所                |                                        |

| 株式会社アナジックス                  | http://www.anagix.com                  |

| 【賛助会員】           |                                  |

|------------------|----------------------------------|

| 株式会社半導体理工学研究センター | http://www.starc.jp/index-j.html |

| 株式会社図研           | http://www.zuken.co.jp           |

| 【学術会員】                      |                                           |

|-----------------------------|-------------------------------------------|

| 早稲田大学 情報生産システム研究科 教授 渡邊 孝博氏 | http://www.f.waseda.jp/watt/              |

| 早稲田大学 井上 靖秋氏                | http://www.f.waseda.jp/inoue_yasuaki/     |

| 中央大学 理工学部 教授 築山 修治氏         | http://www.elect.chuo-u.ac.jp/tsuki/      |

| 神戸大学 大学院システム情報学研究科 教授 永田 真氏 | http://www.cs26.scitec.kobe-u.ac.jp/~lsi/ |

| 高知大学 理学部 教授 村岡 道明氏          | http://www.is.kochi-u.ac.jp/~muraoka/     |

| 【個人会員】                    |  |

|---------------------------|--|

| ワイズ・テクノコンサルティング事務所 山本 節雄氏 |  |

(会員番号順)

# JEVeC について

| 主な活動      | ネットワーク作り   | 四半期毎に会員および関係者も参加できる理事会を開         |

|-----------|------------|----------------------------------|

|           |            | 催し、会の活動に関する意見交換および情報交換を行         |

|           |            | っています。また、他団体(NEDIA や PMJ、JASA 等) |

|           |            | との連携や情報交換も行っています。                |

|           | JEVeC スクエア | 毎年秋頃に会員と半導体・電子機器メーカー関係者を         |

|           |            | 招待して講演会・交流会を行っています。              |

|           | 総会         | 毎期5月に全会員が集まって、会の活動報告、活動方         |

|           |            | 針を決定する総会を行っています。                 |

|           | 紹介冊子の発行    | 会員の事業/製品/サービス/研究内容を紹介する冊子を       |

|           |            | 発行しています。                         |

| 会員種別      | 正会員        | 本会の主旨に賛同して入会する EDA を自ら開発し事業      |

|           |            | としているベンチャー企業または企業内部門、EDA 関       |

|           |            | 連研究開発団体                          |

|           | 賛助会員       | 前項に該当しないもので、本会の主旨に賛同する機関、        |

|           |            | 法人および個人                          |

|           | 学術会員       | 大学、企業等の EDA 関連研究機関または研究者         |

|           | 個人会員       | 本会の趣旨に賛同する個人                     |

| 2014 年度役員 | 会長         | 本垰秀昭(TOOL 株式会社)                  |

|           | 副会長        | 中島義弘 (株式会社アストロン)                 |

|           |            | 小篠隆宏 (ケイレックス・テクノロジー株式会社)         |

|           | 理事         | 太田裕彦(株式会社ジーダット)                  |

|           |            | 水田千益(株式会社 NTT データ数理システム)         |

|           |            | 若林一敏 (日本電気株式会社)                  |

|           | 監事         | 市川幸男 (株式会社東京システム技研)              |

|           |            | 篠塚一也(有限会社アートグラフィックス)             |

|           |            |                                  |

# <入会のご案内>

本会にご興味のある方、入会を検討、ご希望される方は下記事務局までご連絡下さい。 事務局

〒103-0004 東京都中央区日本橋 3-4-14 OZAWA ビル

株式会社ジーダット内 太田裕彦

TEL:03-5847-0312

FAX:03-5847-0315

E-mail: <a href="mailto:jevec.info@jedat.co.jp">jevec.info@jedat.co.jp</a>

# **JEVeC**

Japan EDA Venture Consortium

# 連絡先

(株)ジーダット内

c/o Jedat Inc.

TEL:03-5847-0312 FAX:03-5847-0315

E-mail: jevec.info@jedat.co.jp

URL: <a href="http://www.jedat.co.jp">http://www.jedat.co.jp</a>

# 所在地

〒103-0004

東京都中央区東日本橋 3 丁目 4 番 14 号

OZAWA ビル

OZAWA Bldg.

3-4-14, Higashi-Nihonbashi, Chuo-ku,

Tokyo 103-0004 Japan