HOT TOPIX

次世代カスタムチップのためのレイアウトの自動化 SpringSoft社

スケマティック・ドリブン・レイアウト(SDL)を強化するデバイス生成技術

SpringSoft社‐Rich Morse著

ICデザインフローでのほとんどの工程と同じように、カスタム・レイアウトは、ますます面倒で、複雑かつ時間のかかるものになってきています。ダイサイズの拡大や、厳しい納期、新しいプロセスによるレイアウト制約に対応するには、常にデザイン・プロセスの自動化を進めていく必要があります。スケマティック・ドリブン・レイアウト(SDL)は、デザイナーがアナログ/デジタル回路をカスタム・フィジカル・インプリメンテーションするのに役立つ自動化機能です。SDLは、回路情報とレイアウト間の継続性を自動的に維持することにより、遥かに速くレイアウトを実現させる。SDLは、スケマティックから自動的にフィジカル・レイアウトを作成するデバイス生成技術に左右されます。

通常のデバイス生成技術は柔軟性に欠けているため、SDLはますます複雑になり、使用が難しくなってきています。また、より複雑なアナログ/カスタム・デジタルICデザインでは、役に立ちません。最先端のデバイス生成技術では、より柔軟で、自動化されたコントロール可能なSDLフローを実現することにより、SDLは単なるドラッグ・アンド・ドロップによるデバイス生成以上のものになっています。レイアウト自動化システムでSDLを利用することにより、レイアウトの密集度やデザイン・スタイルに妥協することなく最適なレイアウトを作成する上で、より効率的かつ効果的な方法を使用することが可能になります。

■SDLの進化

過去数年に渡り、カスタムICデザイン・プロセスは、手間のかかる回路の手書き作業から、増加する膨大なデータを処理するために、セルモデル(デバイスまたはデバイスグループ)や階層設計を用いるポリゴン・レイアウト・エディタの使用へと進化してきました。その後、スケマティック・エディタが加わり、ワークステーションでグラフィカルに回路設計を行えるようになっています。けれども、回路設計者からレイアウト設計者への設計意図の伝達は未だに難しく、時間と労力のかかる詳細な回路図のレビューも必要であり、さらに、手作業でデバイス属性をレイアウトへトランスレートしなければならない。レイアウトvsスケマティック(LVS)及びデザインルールチェック(DRC)等のコンピュータ・プログラムは、接続性/配線エラー(LVS)やルール違反(DRC)を検出するために導入されました。

ロジック回路図からフィジカル・レイアウトを自動的に生成できるSDLは、生産性を大幅に向上させました。SDLフローでは、回路図内のコンポーネントを選択し、レイアウト・エディタへ「ドラッグ」すると、自動的にフィジカル・デザインが作成されます。

アナログ/カスタム・デジタルIC設計者は、特定のデバイスに対応するシンボルを使用して回路図を作成します。設計者は、レイアウトの前に、ファウンダリから提供されたモデルを使用してシミュレートした結果に基づき、様々なパラメータに値を割り当てます。カスタム・レイアウト・デザインの場合、最適なパフォーマンスと可能な限り高密度なレイアウトのデザインを作成するために、柔軟な設定が必要になります。従って、設計者は通常、様々なデバイス・サイズが必要になります。つまり、実用的かつ自動化されたSDLフローを作成するためには、それぞれのデバイスに対して何百、場合によっては何千もの異なるパターンが必要になるのです。

SDLメソドロジは、パラメータ化されたセル(PCell)を用いて、異なるデバイス・パターンの条件に対応する。PCellは、規定のパラメータに基づいてフィジカル・レイアウトを定義するソフトウェア・スクリプト(コマンド配列)です。単体のPCellは、指定されたディメンジョン変数やパラメータに異なる値を代入することにより、多くの固定セルの代用として扱えます。独自のフォーマットで最初に書かれたスクリプト(Tclなどの業界スタンダードのフォーマットを使用しても書くことができる)は、セルのインスタンスがデザインに使用された場合に、レイアウトツールが何をすべきかを表します。一方、パラメータは、そのインスタンスのディメンジョンを定義するために、スクリプトで指示された変数値を表します。

SDLメソドロジを用いてPCellを配置する場合、追加情報を入力したり、接続情報を割り当てることなく、回路設計者が回路図内に指定したパラメータと接続情報を反映したレイアウトが自動的に生成されるので、時間を大幅に節約することができます。

SDLとPCellの組み合わせは有益ですが、従来のSDLフローを使用している設計者は、PCellの設定(設定には、スクリプトの記述やフローの構築が含まれる)や使用に必要な時間や労力と、より迅速にレイアウト結果を出すという究極の目標とのトレードオフを考慮することに着目する。多くのレイアウト設計者は、必要な結果を出すために、最終的には複雑な自動システムを信用するよりも、慣れた手作業を選択します。今日のアナログ/カスタム・デジタルIC設計者が必要としているものは、どれ程の頻度で、どれだけの自動化を適用するかをコントロールするだけではなく、プロセスのコントロールもできる手法です。このメソドロジは、デザイン・スタイルやレイアウト結果の質を損なうことなく、最高の手動レイアウトと同等のレイアウト結果を実現するために、シンプルかつ直観的でなくてはなりません。

■コントロール可能な自動化と最先端デバイス生成

デジタル設計で使用されている自動配置配線フローで、現在利用可能な自動化技術は、カスタムICデザインには適していません。カスタムIC設計者が必要としているものは、ワークフローから面倒で非生産的な行為を取り除き、設計者の専門知識を強化するコントロール可能な自動化技術です。SDLメソドロジにおける次の改革は、より少ない労力でより迅速なレイアウトを実現できると同時に、SDLフローでコントロール可能な自動化の必要性に対応することです。具体的には、最も普及しているPCellにおいて、時間のかかるスクリプト作成の必要性を排除することです。

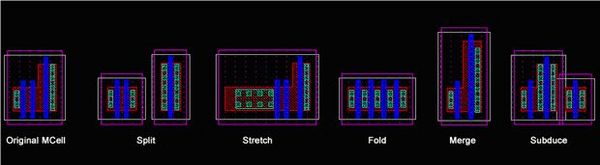

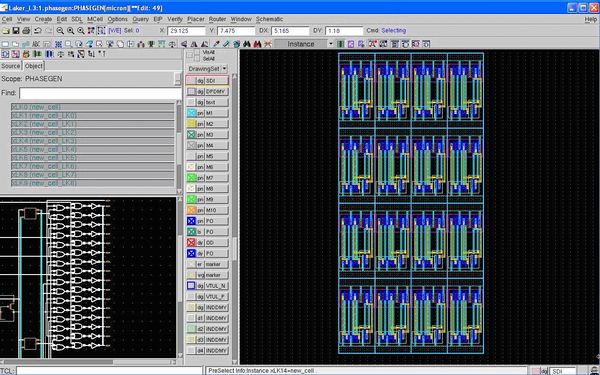

この改革の核となるのは、最適なデバイス・レイアウトを生成できる、より柔軟かつダイナミックな方法が可能なデバイス生成技術です(図1)。この技術は、関連する全ての利点を損なわず、パラメータデバイスをPCellと同様の方法で利用することが可能になります。しかしながら、このようなデバイスは、ファウンダリや、使用されているプロセスや技術には左右されません。デバイスは、タイプ(例:抵抗、コンデンサ、トランジスタ、ガードリング、コンタクト/バイアス)によってカテゴリー化されます。また、EDAツールによってGDSII内のレイアウト・データとして読み取ることも可能です。

図1:より進化したデバイス生成技術により、労力や時間を節約し、最適なレイアウト作成を実現

図1:より進化したデバイス生成技術により、労力や時間を節約し、最適なレイアウト作成を実現

SDLフローを強化するために、より自動化されたデバイス生成アプローチを利用することは、とても魅力的です。また、同時に、より自動化され、かつ完全にコントロール可能なSDLフローも可能になります。ユーザ・フレンドリーなデバイスのプラニング、配線、操作性能によって、直観的なコントロールを実現することができます。

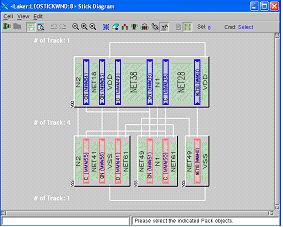

このような機能の一つに、シンボリック・デバイスの最適化があります。これは、ユーザがパラメータやデザイン・ルール、接続性を気にすることなく、シンボリック・レベルでデバイスのフロアプランを最適化することができます(図2)。フロアプラニングが完成し、面積や配線、使用可能なスペースの形状などに対するデザインの最適化を行ったら、フロアプランと適合したデバイス・レイアウトが自動的に生成されます。レイアウトは、回路図内に定義された接続やサイズを維持します。

図2:さらに自動化された技術により、デバイスが象徴的なレベルで、簡単にスワップ、マージ、移動、分割、配列できる"on-the-fly"のデバイス生成や最適化が可能

図2:さらに自動化された技術により、デバイスが象徴的なレベルで、簡単にスワップ、マージ、移動、分割、配列できる"on-the-fly"のデバイス生成や最適化が可能

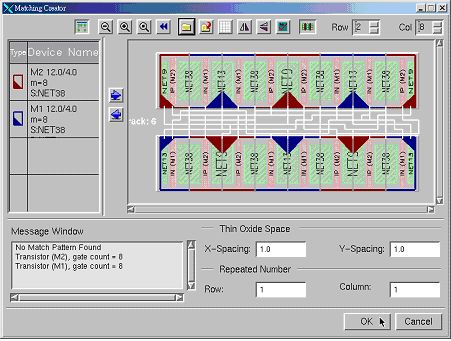

これと同じ技術を、レジスタやキャパシタのレイアウトに応用することができ、マッチングデバイスの問題といった、さらに複雑なレイアウト問題を解決することができます(図3)。マッチング・デバイス・レイアウトは、コントロール可能なSDLフローによって多大な恩恵を得ることができます。というのも、このSDLフローは、シンボリック・レベルやデザイン・ルールに従い自動的に生成されたレイアウトにより、レイアウト・プラニングの重要な課題に対処することが可能だからです。この機能は、特にプロセス変動や回路のノイズに影響を受けやすいアナログ・デバイスにとっては非常に有効で、デバイスを適合させるために必要なプロセス変動の影響を最小化する特別なレイアウト技術が必要になります。

図3: 約40%のアナログ・トランジスタがマッチング・トランジスタで、自動化されたパターン・マッチング機能により、完全にレイアウトをコントロールしつつ、生産性を大幅に向上

図3: 約40%のアナログ・トランジスタがマッチング・トランジスタで、自動化されたパターン・マッチング機能により、完全にレイアウトをコントロールしつつ、生産性を大幅に向上

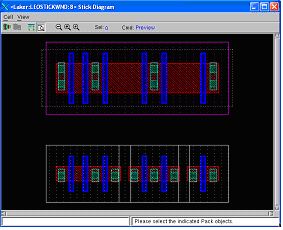

回路の繰り返しパターンを効率的にレイアウトするために、パターンの複製機能によって、SDLフローをさらに自動化することができます。これにより、複数の回路要素をグループ化し、繰り返しパターンを形成し、このグループに対してレイアウトを生成し、デザイン全体の中から自動的に同一のパターンを検出し、生成したレイアウトの回路内での再利用が可能になります(図4)。この機能は、繰り返しパターンのレイアウト速度を大幅に向上します。

さらに、よりコンパクトなレイアウトに対しては、パターン・リユースと呼ばれる技術を利用して、繰り返しパターンを最適化することができます。これは、パターンの複製と同じように機能しますが、繰り返された回路階層を平坦化することができ、前述のSDLフローを使用してフルカスタム・レイアウトを実行することができます。この方法は、SDLを使用したフルカスタム・レイアウトの利点全てを得られるだけではなく、パターン複製のスピードを向上させることができます。パターン・リユースを使用することにより、平坦化された回路は、スケマティック・ビュー自体に影響を与えることなく、完全な接続性とクロスプロービング機能を維持することが可能です。

図4: Lakerソフトウェアシステムに搭載された「Copy&AssociateとPattern Reuse」機能が、繰り返しパターンのレイアウト速度を大幅に向上

図4: Lakerソフトウェアシステムに搭載された「Copy&AssociateとPattern Reuse」機能が、繰り返しパターンのレイアウト速度を大幅に向上

■最後に

スケマティック・ドリブン・レイアウトは、今日のアナログ/カスタム・デジタルIC設計者にとって、多くの利点があります。しかし、コントロールできない自動化は、しばしば、設計者に、設定時間とレイアウトスピードの好ましくない二者択一を迫ります。柔軟なデバイス生成技術は、最先端SDLフローでコントロール可能な自動化を実現することで、この課題に対応しています。この技術は、設計者が自動化をよりコントロールすることができるだけでなく、広範な機能を使用して、時間と労力を大幅に削減すると同時に、より優れたレイアウト結果を出すことができます。回路設計の規模が拡大し、さらに複雑になっていく中、このような機能は、今日および今後のアナログ/カスタム・デジタルICの設計を納期どおりに製品化し、競争に生き残っていく上で必要不可欠となるでしょう。

■著者について

Rich Morse氏は、SpringSoft社のカスタムICデザイン・プロダクトの技術マーケティング・マネージャー兼EDAアライアンス・マネージャーです。

お問い合わせ:株式会社スプリングソフト

|ページの先頭へ|