HOT TOPIX

ルネサスがCadenceのDRCツールでアナログIPレイアウトのTAT削減に取り組む

2012年7月20日、Cadenceのユーザー・カンファレンス「CDN Live! Japan」がみなとみらいで開催された。

ここでは同セミナー行われたセッション「アナログIPレイアウト設計効率改善 In-Design DRC ツール Virtuoso IPVSの適用」について紹介する。

講演を行った、ルネサス エレクトロニクス株式会社 技術開発本部 EDA・設計手法統括部 アナログ設計技術開発部の小林裕氏によると、近年プロセスノードの微細化によって、アナログIPレイアウト設計におけるDRC検証とエラー修正期間が増大しつつあり、今後それはさらに増え続けると予想されている。

なぜDRC検証とエラー修正期間が増えるかと言うと、微細化によって複雑な条件付きルール数が増えているためで、それらルールによってDRCエラーが増加し、エラーの修正が更なる周辺のエラーを呼びエラー修正が収束せずTATが増大している。

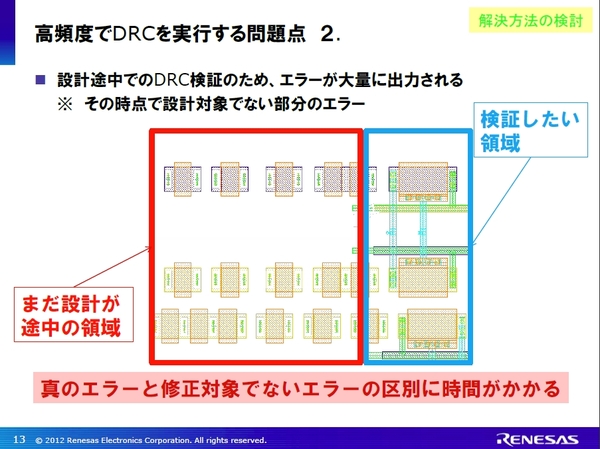

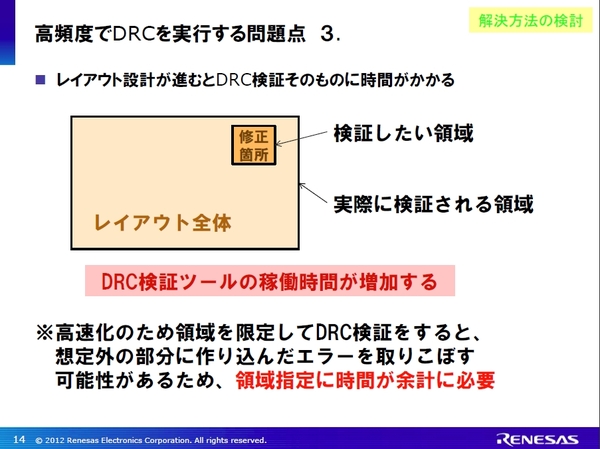

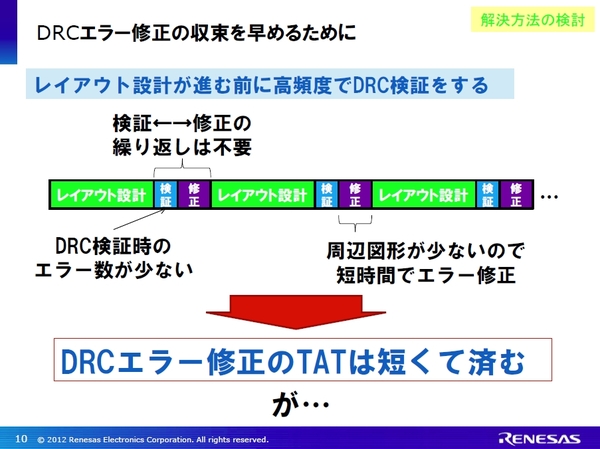

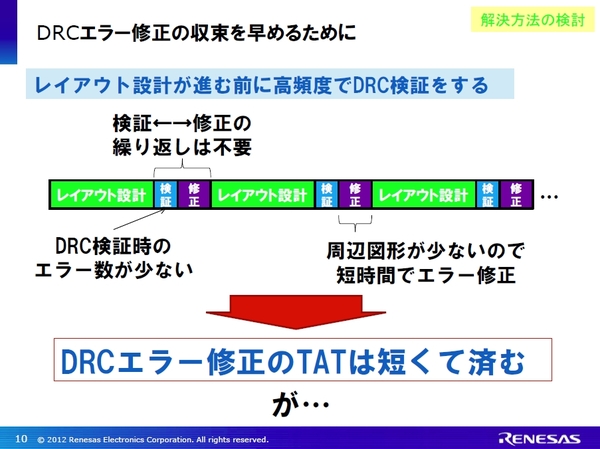

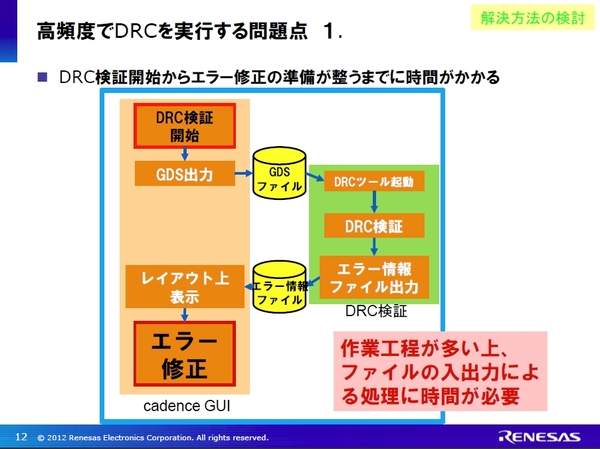

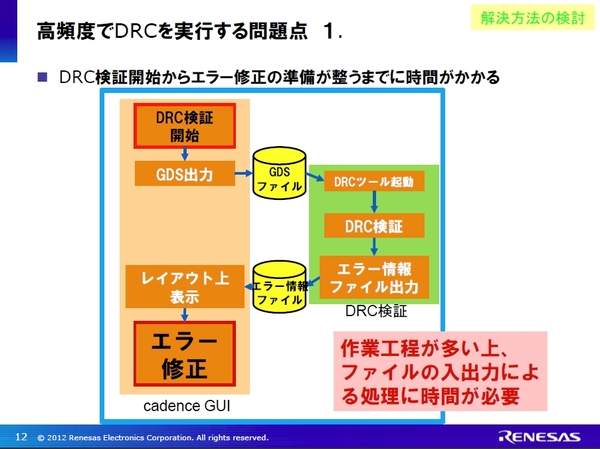

そんな状況を改善するために小林氏は、レイアウト設計が進む前に高頻度でDRC検証を実施するというアプローチを考えた。レイアウト初期段階でDRCを実施すればエラーの数が少なく、周辺図形も少ないため短時間で修正作業が済み、検証と修正のイタレーションが不要になるなど、確実にDRCエラー修正のTAT短縮が見込める。しかし、このアプローチにはおいても問題は幾つかあった。

※画像はルネサスエレクトロニクス小林氏の講演データ

まず、DRC検証の開始からエラー修正に着手するまでの作業工程が多く、ファイル入出力の時間、ツールの起動時間などとにかく時間が掛かってしまう。また、これから作る部分も含めて全体的にDRCをかけると、検証対象外のエラーも出てしまいエラーの選別が必要になる。更に設計が進んでいくとレイアウト全体にDRCかけることになり、結局ツールの処理時間が増えることになる。実際に使用していたDRCツールで試したところ、想定したTAT短縮効果は有ったが、ツール側のオーバーヘッドにより効果は相殺されてしまった。

※画像はルネサスエレクトロニクス小林氏の講演データ

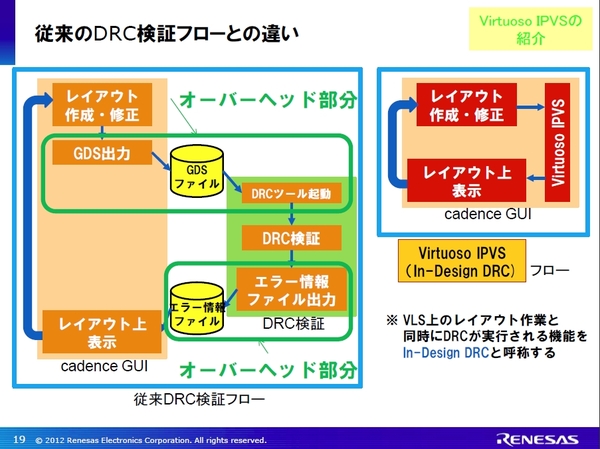

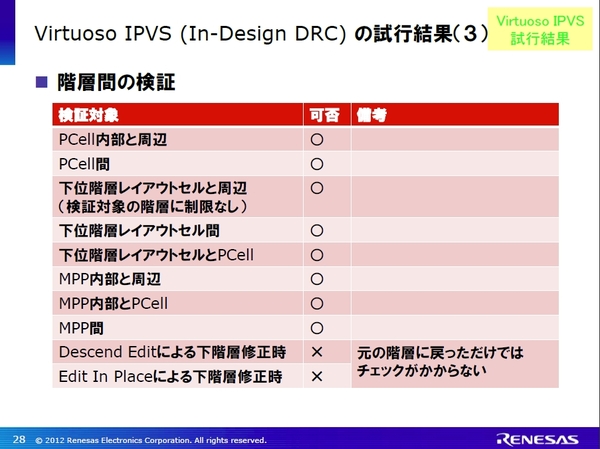

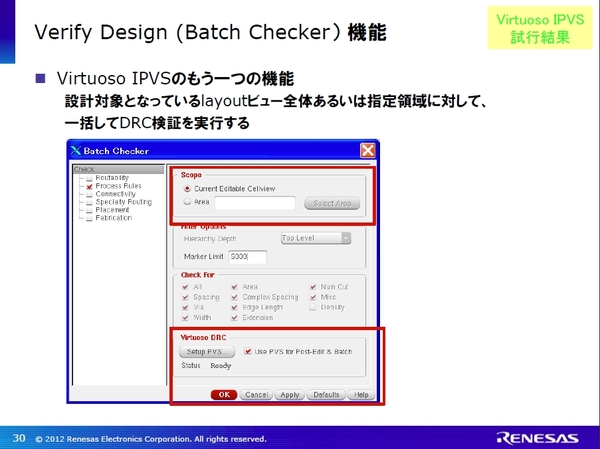

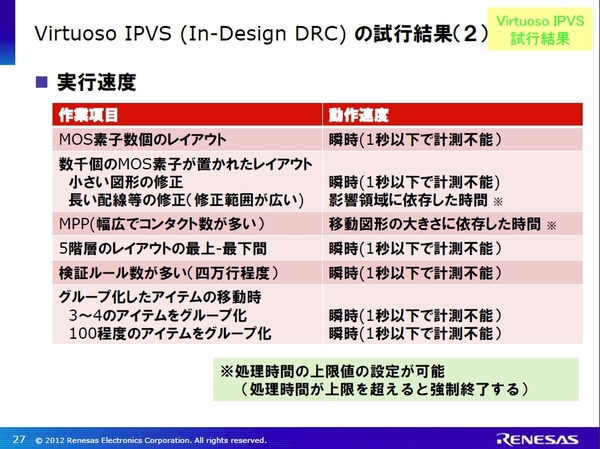

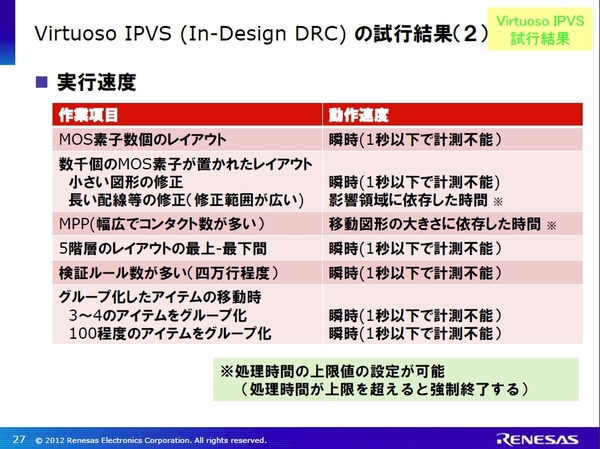

そこで小林氏はCadenceのDRCツール「Virtuoso IPVS」を使用する事にした。「Virtuoso IPVS」であれば、ファイル変換不要で設計データを直接検証可能で、検証対象を限定でき、サインオフツールと同精度の検証が可能なためである。また「Virtuoso IPVS」は、レイアウト作業と同時にDRCエラーを検証可能(In-Design DRC)で、複雑な条件付きルールにも対応しているため所望のTAT短縮効果を得るには最適なツールと言えた。

※画像はルネサスエレクトロニクス小林氏の講演データ

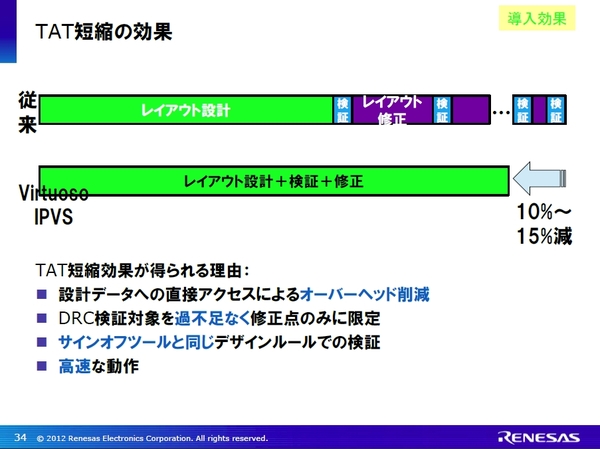

実際に「Virtuoso IPVS」を試行しその実行速度や適用範囲、In-Design DRCと一括DRC機能の組み合わせ利用などを確認したところ、その導入効果として従来比10-15%程度のTAT短縮効果が得られるという結論に至った。また小林氏によると、先端プロセスのデザインに限らず太いノードのプロセスにおいても、「Virtuoso IPVS」を用いることで短TATで小面積なレイアウトが可能な事を確認できたという。

※画像はルネサスエレクトロニクス小林氏の講演データ

|ページの先頭へ|