HOT TOPIX

SystemC Japan 2013ユーザー事例講演、DSP設計に高位合成を適用したルネサス

2013年6月21日、今年で8回目の開催となるセミナー「SystemC Japan 2013」が開催された。

同セミナーは、設計言語IEEE 1666 SystemCにフォーカスした技術セミナーで、主催はSystemCの仕様策定および普及活動を推進する業界団体米Accellera Systems Initiative。SystemC関連のセミナーとしては世界最大の開催規模を誇っている。

ここでは、SystemC Japan 2013で発表されたルネサス エレクトロニクスのユーザー事例の内容を紹介する。

■ルネサス エレクトロニクス「高位設計技術によるDSP設計効率化の取り組み」

ルネサス エレクトロニクスの講演は、第一事業本部 システムインテグレーション事業統括部 FE設計技術開発部 主任技師の大坪 基秀氏。今回大坪氏が紹介してくれたのは、DSP設計における高位合成ツールの適用例で、使用したツールはCadenceの「C to Silicon Compiler」。ルネサスでは既にデータパス系の回路の設計で高位合成の利用が定着しており、制御系の回路に関しても適用フェーズに入っている状況で、データパスと制御が混在するDSP設計への高位合成の適用は新たなチャレンジだった。

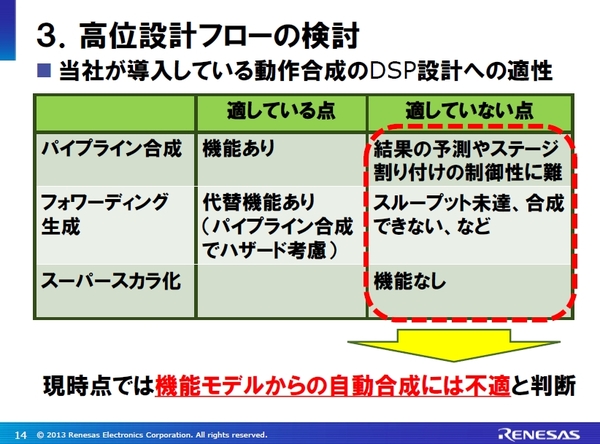

大坪氏が示したDSP設計のポイントは3つ。

1.スループット向上のためのパイプライン処理

2.パイプライン処理によるデータハザード解消のためのフォワーディング処理

3.リアルタイム性向上のためのスーパースカラ化

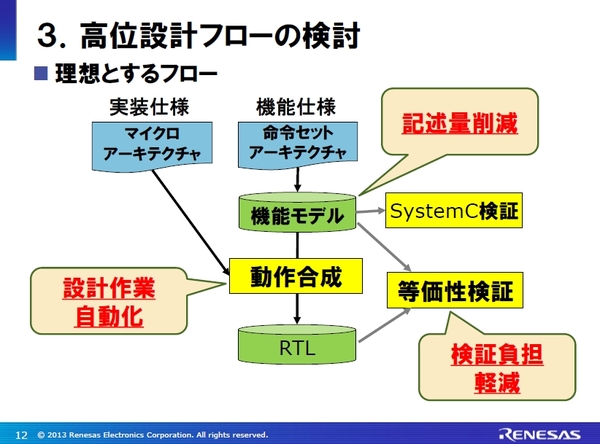

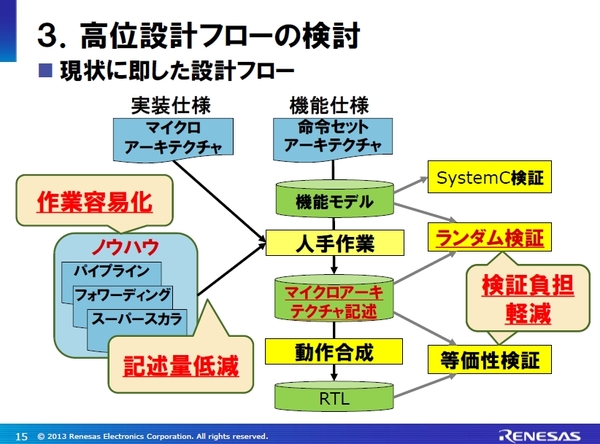

これらを設計で実現しようとすると、デザインが複雑となり記述量も増大、検証も難しくなるため、一連の問題を高位合成と等価性検証を用いて解決しようと設計フローを検討したが、現時点では機能仕様(からおこしたSystemCの機能モデル)からの自動合成は無理と判断。DSPのマイクロ・アーキテクチャを人手で作りこんだSystemC記述から合成することにした。

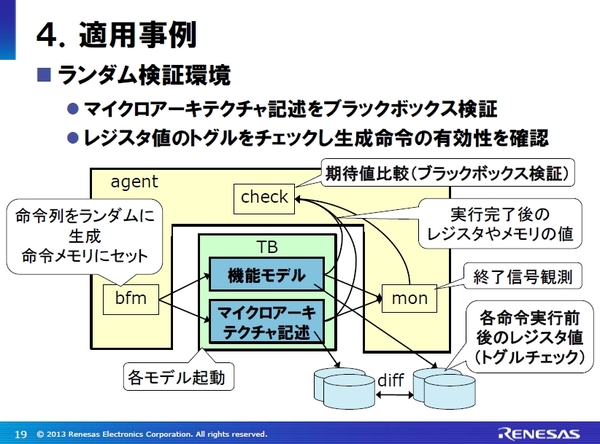

実際に高位合成を適用したのは、2Wayスーパースカラ構成、3ステージパイプラインのプロセッサ部で、合成用のマイクロ・アーキテクチャ記述のコーディングは、記述パターンをノウハウ化して作業を効率化。その検証にはCadenceのランダム検証「Specman」を適用し、合成結果との等価性検証にはCalypto社の「SLEC」を使用した。

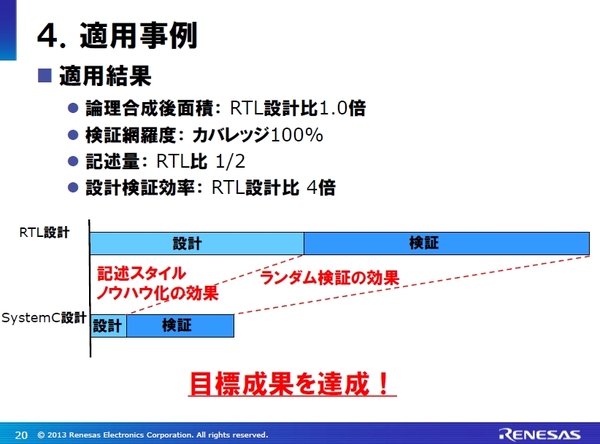

その結果、回路面積、検証網羅度、コード記述量、設計検証効率の全てにおいて当初目標を達成(下図参照)。設計検証効率の大幅な向上には、SystemCコーディング・スタイルのノウハウ化とランダム検証が大きく貢献した。(ちなみに、コーディング・スタイルのノウハウ化には2週間程度の工数を費やしたとの事。)

ランダム検証では、元の機能モデルと人手でリファインメントしたマイクロ・アーキテクチャ記述のそれぞれのランダム検証結果を比較し動作を確認。特にフォワーディングの箇所についてはカバレッジを取り100%のカバレッジを確認した。また、レジスタの更新状況を確実に確認するために、各命令前後のレジスタ値の履歴を取りトグルチェックを行った。

※スライド資料は全てルネサス提供のデータ

大坪氏は、今後の課題として、理想的なフローと考える機能モデルからの合成の実現を挙げ、これにはEDAベンダのツール強化に期待するとした。講演の最後には、高位合成の適用拡大に向けては社内へのプロモーションやエバンジェリストの育成も重要とコメントし、将来的には高位合成によるインターコネクト生成にも取り組みたいと抱負を語った。

|ページの先頭へ|