HOT TOPIX

CadenceLIVE Japan 2023参加レポート(2)、ルネサス、キヤノンによるAIツール活用設計の事例

2023年7月14日、Cadenceはユーザー・カンファレンス「CadenceLIVE Japan 2023」をみなとみらいのホテルで開催した。

ここでは前回のレポート【RTL設計の次世代新製品「Joules RTL Design Studio」発表】に続き、AI技術を用いた事例発表のレポートとして、ルネサスエレクトロニクスならびにキヤノンの事例を紹介する。

■ルネサス エレクトロニクスによるビッグデータ解析PF「JedAI」活用事例の紹介

ルネサスエレクトロニクスの藤井 孝氏(オートモーティブソリューション事業本部 車載プラットフォームLMT事業部 車載バックエンドプラットフォーム部 部長)は、「Big Data Analytics Platform JedAIを用いたP&R工期短縮取り組みと今後の展望」と題して、同社とCadenceで共同開発したタイミング解析アプリ「Silicon Sights」について発表を行なった。

藤井氏の講演風景

藤井氏によるとタイミング解析アプリ「Silicon Sights」は、Cadenceが提供するAIベース・チップ設計向けのビッグデータ解析プラットフォーム「JedAI(Joint Enterprise Data and AI Platform)」を活用して開発したもの。同社では既にP&RにおいてCadnceのAIベース最適化ツール「Cerebrus」を活用して工数のかかるPPAの改善に成果を上げているが、同じく工数のかかる複雑な回路ブロックやMCUなどのデバッグ工数を削減すべく、タイミングレポートを元に「何を治せばいいのかJedAIに解決してもらう」という発想でツールの開発を進めた。

現在実現している「Silicon Sights」の基本的な機能は、タイミングの違反を複数のカテゴリに分類、カテゴリごとにパスの違反を表示しその詳細、原因、階層などの情報を提供してくれるというもの。タイミング違反を時系列で表示することもできる。これを利用すればタイミングレポートを一つ一つ追わなくても、出てきた情報を元に対策を打つことができると藤井氏。ゆくゆくはレイアウトを分析するための指標を組み合わせ、タイミング解析にあたりレイアウト上の問題が一目でわかる形、更には対策案を自動的に提示してくれる形を目指したいと語っていた。

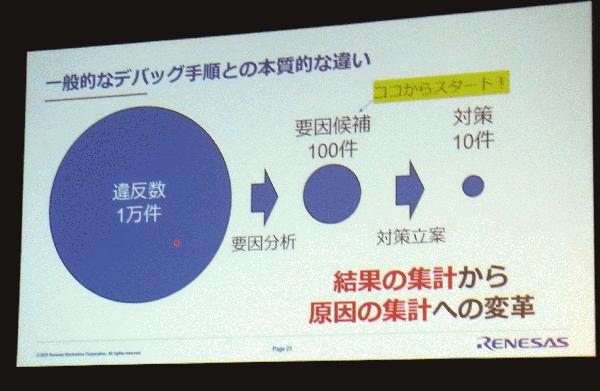

まとめとして藤井氏は、一般的なデバッグ手法と今回開発した「Silicon Sights」を用いたデバッグ手法の本質的な違いはその出発点にあるとし、従来行っていたタイミング違反の集計をスキップして、違反の要因集計からデバッグを開始できると説明。それによりP&Rにおけるデバッグ期間を約3割短縮できる見込みとした。

さらに将来的な展望として、P&Rを行いながら同時にデバッグも行うという「リアルタイムデバッグシステム」の実現など設計の自動化を積極的に進め、2〜3年以内には100Mインスタンスの設計ブロックを一人のエンジニアが設計できるようにしたいとコメント。「設計の自動運転のハンドルはユーザーが握っている」というメッセージを残して発表を終えた。

なお藤井氏によると今回Cadenceと共同開発した「Silicon Sights」は、近いうちに何らかの形で他社ユーザーも利用できるようになる予定だという。

■キヤノンによるAIベース最適化ツール「Cerebrus」活用事例の紹介

キヤノンの佐々木 誠仁 氏(デバイス開発本部 半導体デバイス第二開発センター 半導体デバイス製品第三設計部)は、「Cerebrusを用いたCMOSイメージセンサーのデジタル回路に対するPPAの改善」と題した事例発表を行った。

佐々木氏の講演風景

佐々木氏によると、開発している積層型のフルサイズCMOSイメージセンサーは、一般的なSoCよりもダイ面積が大きくアナログ回路が面積の40〜50%を占め、デジタル回路のアスペクト比が非常に高いため、P&Rやタイミング収束が非常に難しいのが特徴。更に昨今はTAT短縮や消費電力の削減要求もあり、より最適なPPAの実現に向けて設計パラメータを効率的に導くソリューションが必要だと考え、Cadenceの「Cerebrus」の適用に至った。

同社が「Cerebrus」に期待したのは「イタレーションの低減」と「最適な設計パラメータの探索」、そして「最適なマクロセル配置の探索」の3つ。「イタレーションの低減」については、インプリメント・フローにおいて最も工数がかかっていた配置配線ツール「Innovus」のイタレーション低減に期待。「最適なマクロセル配置の探索」については「Cerebrus」の「Floorplan Explorer」により探索の自動化による工数の削減に期待した。佐々木氏によるとイメージセンサーではマクロセルが数百にもおよび、その配置の試行錯誤に多くの工数を要していたという。

実際にCMOSイメージセンサーのデジタル回路設計に「Cerebrus」を適用した結果として、佐々木氏は下記3例を報告した。

1. 「Cerebrus」を用いて「Innovus」によるPPAの最適化を実施した例(1)

呼び出し回路層のデジタル回路ブロック(アスペクト比の高い回路で短辺側に1,000もの信号線が存在、約5Mゲート、マクロセル248個)の設計において「Cerebrus」を適用したところ、従来の「Cerebrus」を用いない手法よりも消費電力を約13%削減することに成功。従来手法よりも30%近い工数削減効果を得ることができた。同回路の設計は、少ない空間を使ってマクロセルを回避しながら配線する必要がある難易度の高いものだったという。

2. 「Cerebrus」を用いて「Innovus」によるPPAの最適化を実施した例(2)

同じくアスペクト比の高い小規模なデジタルブロック(268Kゲート)の設計において「Cerebrus」を適用したところ、従来の「Cerebrus」を用いない手法よりも配線長を8%、消費電力を2.1%削減することに成功。従来手法よりも10%近い工数削減効果を得ることができた。

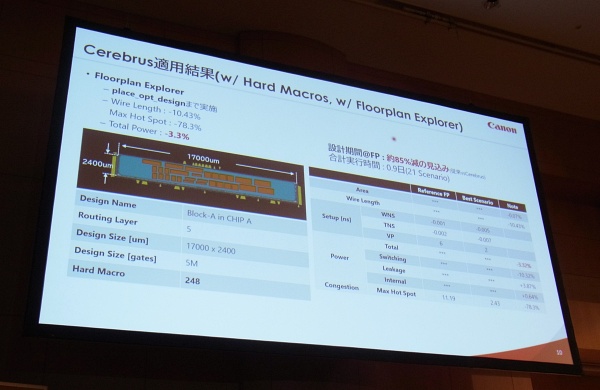

3. 「Cerebrus」の「Floorplan Explorer」で配置の最適化を実施した例

上記事例1と同じデザインに対してPPAの最適化は行わず「Floorplan Explorer」で配置の自動最適化を実施したところ、配線長を約10%、消費電力を約3%削減でき、ランダムでありながら最適なマクロセルの配置結果を得ることができた。21シナリオの実行に要した時間は0.9日で従来手法よりも85%近い工数削減効果を得ることができた。

佐々木氏によると「Cerebrus」を使って設計したデザインはすでにテープアウトを完了しているということで、今回の結果を受けて今後は「Cerebrus」を論理合成「Genus」やタイミング解析「Tempus」にも適用していきたいとコメント。Cadenceのインプリメント・フローを利用していれば「Cerebrus」を容易にフローに導入・統合できると付け加えた。

なおキヤノンではCadenceの協力を得て「Cerebrus」による最適化に「歩留指標」を加えること、電源配線の最適化に「Cerebrus」を活用することなどに取り組んでいるとの話だった。

|ページの先頭へ|