HOT TOPIX

CadenceLIVE Japan 2023参加レポート(1)、RTL設計の次世代新製品「Joules RTL Design Studio」発表

2023年7月14日、Cadenceはユーザー・カンファレンス「CadenceLIVE Japan 2023」をみなとみらいのホテルで開催した。

コロナ禍以降、数年ぶりに従来の形で開催された今年の「CadenceLIVE Japan 2023」。参加登録者数は900名近くを数え会場は非常に多くの参加者で溢れていた。

CadenceLIVE Japan 2023 イベント会場の様子

ここでは当日行われた計35のセッションのうち、基調講演および新製品発表関連のセッションを中心にイベントの様子を紹介したいと思う。

■日本ケイデンス 金子社長の挨拶

冒頭で挨拶を行ったCadence日本法人の金子社長によると、Cadenceの業績は非常に好調で2022年Q2においてはIPなどを除くEDAコア・ソフトウェアの売上でトップシェアを獲得。2021年リリースのAIベースのデジタル設計自動最適化ツール「Cerebrus」が市場で高く評価されており、「Cerebrus」を用いてテープアウトされたチップは既に180品種を超えているという。この実績は競合のSynopsysが今年2月に発表したAIベース・ツールによるテープアウト実績「3年間で100品種」を上回る勢いだ。

その他にもエミュレーターなどハードウェア・ベースの検証システムが前年比20%増の成長、同社が力を入れているシステム分野のツール群が前年比30%増の成長など、主力のソリューションが軒並み好調。今年に入って投入したAIベースのアナログ/カスタム設計ツール「Virtuoso Studio」にも大きな期待を寄せているという。

■基調講演:Cadence本社 Chin-Chi Teng氏、RTL設計の次世代新製品「Joules RTL Design Studio」発表

「Intelligent System Design戦略を加速するComputational Software技術」と題した、米国Cadence本社のChin-Chi Teng氏(PhD, Digital & Signoff Group Senior Vice President and General Manager)の基調講演は、AIをベースとしたシステム設計に関する同社の取り組みを説明するものであった。

Chin-Chi Teng氏の講演風景

Chin-Chi Teng氏によると同社の顧客の約45%はシステム企業でその市場規模は半導体市場を大きく上回る約3兆ドル。半導体企業だけではなくシステム企業にもソリューションを提供しているという意味で今後の業績については楽観的だとコメント。コンピュータ・サイエンスと数学を用いたデータ最適化に長年取り組んできた同社は、そのソリューションをバイオ分野など周辺領域にも拡げていく計画だという。

EDAという技術に関しては、チップ上のトランジスタ数が1兆個に到達すると言われる2030年に向けて、AIをベースとした多くの自動化が必要になると指摘。それは「新たなEDA業界の始まり」であると語り、「JedAI」をはじめとした既に実現している同社のAIベース・ソリューションについて説明した。その説明の中で紹介されたのが「Joules RTL Design Studio」というRTL設計のための新製品だ。

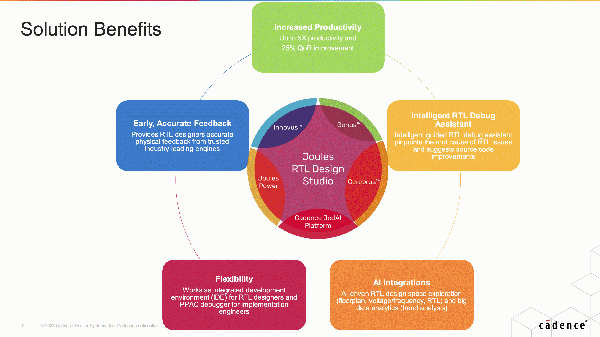

米国で開催されていた第60回Design Automation Conferenceと重なり今回ちょうど良いタイミングで発表された「Joules RTL Design Studio」は、Cadenceが放つ大型の次世代製品で大げさに表現するとRTL設計のパラダイムシフトを目指すもの。詳細については後述するが、フィジカルを考慮した高精度なRTL設計を支援する同ツールは、RTL設計の収束を最大5倍高速化しQoRを最大25%改善するという驚きのパフォーマンスを備えている。

Chin-Chi Teng氏は新製品「Joules RTL Design Studio」も含め、同社のデジタル設計ソリューションの強みは複数のコアエンジンをパラレルに動かしフルフローのインテグレーションを実現できる点だと主張。その総合力とAI技術を用いたQoRの高さを強調していた。

なおシステム分野のソリューションについては、Chin-Chi Teng氏曰く、EDA分野でやってきたことの応用で数々の成功を収めており業績は急成長中。米スタンフォード大からGPUの専門家チームを獲得するなど人員増強も進めており、今後はまだ誰もやっていない「システム解析の最適化」に取り組みシステム分野における革新を目指すと語った。

余談だが、Chin-Chi Teng氏の基調講演の中でNVIDIA CEOのJensen Huangの動画が流された。Jensen Huang氏は「Grace Hopper」を片手にNVIDIAはCadenceのビッグカスタマーでありCadenceの全てのツールを活用すると同時に、「Grace Hopper」でCadenceツールを動かすことに取り組んでいると語っていた。

■新製品「Joules RTL Design Studio」とは?

今回のイベントの目玉の一つとなった新製品「Joules RTL Design Studio」については、米国本社から開発責任者のYufeng Luo氏とKamlesh Madheshiya氏が来日し、セッションを通じて製品の説明を行なった。

Yufeng Luo氏による説明のポイントをまとめると、「Joules RTL Design Studio」は以下のような製品となる。

・RTLの最適化に焦点を当てて開発された製品でユーザーは全てのRTL設計者(インプリメント・エンジニア含む)

・複雑なデザインで起こりうる配線混雑やタイミング違反の原因はRTLか?それとも配置か?という問題を早期に解決

・RTL設計フェーズでバックエンド処理のフィードバックを得ることが可能

・レイアウト設計の知見が無いRTL設計者でもレイアウトを考慮した高品質なRTLを設計可能

・デザインの収束を最大5倍高速化しQoRを最大25%改善

画像はCadence提供のデータ

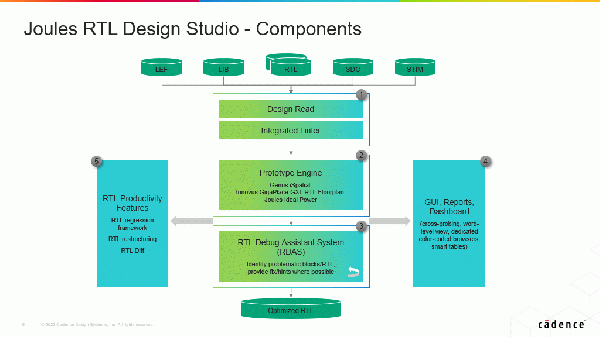

「Joules RTL Design Studio」のコアな技術として挙げられるのは、同社の論理合成「Genus」、配置配線「Innovus」、パワー解析「Joules」の各エンジンをツールに内蔵している点で、これによりバックエンド工程にRTLを渡す前にツール内で高精度なプロトタイピングが可能。その結果を元にRTLを最適化することができる。

最適化に用いるのは「RDAS(Intelligent RTL Debugging Assistant System)」と呼ばれるインテリジェントなデバッグ機能で、「RDAS」を通じてPPAC (power, performance, area, congestion) のデバッグに必要な可視化された物理情報にアクセスすることが可能。同機能にはタイミング・エラーの要因推定など約20種類の解析・デバッグ機能が備えられているということだ。

従来手法ではRTL設計とバックエンド設計間のイタレーションに多大な工数を要していたが、「Joules RTL Design Studio」を利用することで設計工程間のボトルネックを解消。フィジカル考慮の高品質なRTLを短期間で手に入れ、そこからインプリメントを開始することで、よりPPACの優れたチップをより早く実装できるようになる。

画像はCadence提供のデータ

「Joules RTL Design Studio」の開発を指揮したKamlesh Madheshiya氏は、インプリメントで使用される実績のある各ツールのエンジンを統合し、単一のダッシュボードを通じて「レイアウトを考慮して」デザインを解析・デバッグできるという点が最大のメリットで、同環境を利用することでジュニアレベルの設計者でもシニアレベルの設計者と同等のRTLを設計できるようになるとコメント。

更に来年には「Joules RTL Design Studio」とAI最適化ツール「Cerebrus」およびAIプラットフォーム「JedAI」を統合する予定で、それによりビッグデータと生成AI技術を用いた更に高度なRTLの最適化が実現できるようになるという話だった。

なお補足だが、「Joules RTL Design Studio」には各種解析エンジン、デバッグ機能の他にLintチェック機能も備えられている。

中央左:Kamlesh Madheshiya氏、中央右:Yufeng Luo氏、両脇のお二人は本社マーケティングの方

■ソシオネクストによる「Joules RTL Design Studio」適用事例の紹介

今回、新製品「Joules RTL Design Studio」の先行ユーザーとして、ソシオネクストがその適用事例について発表を行なった。

発表したのはグローバル開発本部 SoCシステム開発部 プリンシパルエンジニア 千綿 幸雄氏。その内容は「Joules RTL Design Studio」のデバッグ機能「RDAS」に焦点を当てたものだった。

千綿氏の講演風景

千綿氏によると7nmプロセス以降、本当の意味で設計がクリティカルな状態になっており、フィジカルを考慮しないと設計を成功できない状況にあるとのこと。そんな状況下で重要なのはデザインの解析で、設計者のノウハウに頼らない新たな手法を模索している中で「Joules RTL Design Studio」のデバッグ機能「RDAS」に着目した。

その理由として千綿氏が挙げたのは下記3点で、同社ではCadenceの論理合成「Genus」で合成した後に「RDAS」で解析を実行。その結果を元にRTLや合成設定、タイミング制約などの対策を実施するという手法を試みた。

・論理合成結果を俯瞰的な視点から整理できる

・バイオレーションの要因から次のアクションを適切に判断できる

・デザインを解析して客観的な指標が提示できる

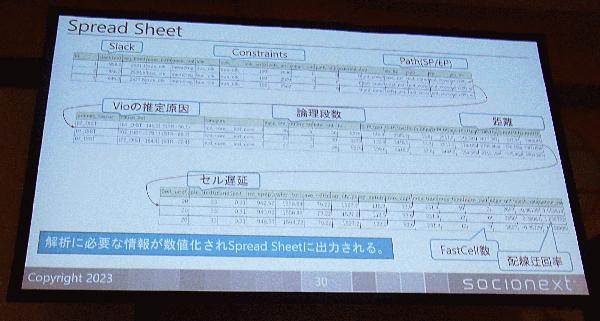

実際に「RDAS」を使ってみた結果、スプレッドシートで出力される解析結果が非常に分かり易く、各バイオレーション・パスに対する論理段数、マンハッタン長、配線長、検証エッジなどを一覧表示で確認することができた。スプレッドシートを覗くことで全体的なバイオレーションの傾向などを把握・分析できるのが大きなポイントと千綿氏。

更にバイオレーションの推定原因を示してくれる点が「RDAS」の大きな特徴だと付け加えた。解析結果の確認・解析からデバッグへの移行は「RDAS」のGUI上で可能で論理合成ツールと同等のデバッグができるという。

画像は千綿氏の講演スライド

千綿氏は「RDAS」は解析のために欲しい情報を全て出してくれるので、対策に向けた次のアクションを簡単に決めることができるようになるとし、合成結果の解析で「RDAS」を活用すれば従来比2〜3倍の生産性を実現できるだろうとコメント。「RDAS」はこれまでの経験を超えたところにある課題の解決に大いに役立つとして発表を締め括った。

|ページの先頭へ|