HOT TOPIX

Mentor Tech Design Forum 2012、CPSに向けたNECの高位合成ツール活用術 ※訂正あり

2012年9月7日、都内でMentorのプライベート・イベント「Mentor Tech Design Forum 2012」が開催され、1000人近くの参加者を集めた。

ここでは同イベントで行われたユーザー講演「CPS向けデータ処理回路を多機種展開するための高位合成活用」の内容をレポートする。

※本記事の内容の一部を訂正致しました。

※本記事の内容の一部を訂正致しました。

本講演を行ったのは、NEC中央研究所の森岡澄夫氏、同氏は古くから高位合成ユーザーとして様々なイベントで発表を行なっている知る人ぞ知る人物。高位合成に限らずハードウェア設計に関する様々な執筆活動もしており、最近ではCQ出版社から同氏の著書「LSI/FPGAの回路アーキテクチャ設計法」が出版されている。同氏は、国内屈指の高位合成ヘビーユーザーと言っても過言ではないハードウェア設計のエキスパートである。

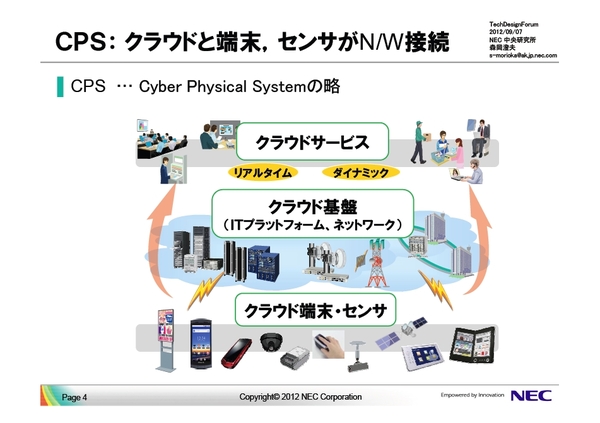

今回森岡氏が講演したのは、講演タイトル通り「CPS(Cyber Physical System)」向けの回路設計に高位合成を適用した話である。講演内容を紹介する前に今回の講演テーマの背景にある「CPS」について触れておきたい。

「CPS(Cyber Physical System)」とは、ここ最近注目されている言葉で、拡大するクラウド・インフラ上に様々なモバイル端末や各種センサーがネットワークを介して繋がる事で、社会の様々な情報がリアルタイムに入手可能となる来るべき高度な情報化の世界を指す。

※画像は森岡氏の講演データ

森岡氏曰く、このような世界の実現に向けては今の技術だけでは課題が多く、大量のデータ処理やリアルタイム応答性の確保などを考えると、インフラでより多くのハードウェア(ASICやFPGA)が利用されるようになるのではないかとの事。既に半導体ビジネスから一線を画しているNECが未だハードウェアに関する研究を行なっているのは、そういった視点によるものでもあるという。

実際にNECでは、サーバーのアクセラレーションIPや顔認識IP、プライバシ保護のための暗号化IP、専用統計処理IPなどの研究開発を行なっており、森岡氏はその開発に高位合成ツールを積極的に活用している。

森岡氏によるとこれまでのハードウェア設計と違い、CPSで使うハードウェアには幾つかの特徴がある。まず、同じアルゴリズムを様々な機器で利用するケースが想定され、性能や電力条件などの違いから、これまでのような同じRTLやチップの使い回しが難しくなる。また、ハードウェアに求められる処理がより複雑になり、精密なアーキテクチャ設計を行わないと狙った性能を出すのが非常に難しくなるという。

森岡氏はそのような背景の中で、高位合成を用いたより効率的なハードウェア設計に取り組んでおり、講演を通じてこれまで培ってきた幾つかの「効果的な高位合成活用術」を紹介してくれた。

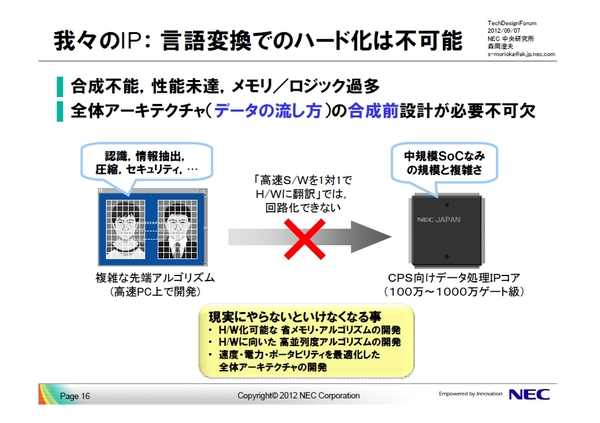

CPS向けのIPの設計にあたり森岡氏が着目しているのは、そのアーキテクチャ設計の重要性。これまでのSoC設計の場合、個々のIPブロックをそれぞれ合成して、それらをバスに繋ぐといった2段階のやり方が主であったが、難しい処理になってくると個々のIPそのものが昔のSoC並の規模になり、性能を出すために個々のIPをどう接続するか?アーキテクチャの問題が非常に重要になってくるとの事。また、様々なアルゴリズムの開発がPC上でソフトで開発されるようになってきており、その規模も複雑なものではC言語で数十万行と大規模化しつつあり、従来とは違う考え方で高位合成を利用しなければ、その活用効果は得られないと指摘した。

例えば、これまでは高位合成を使えばソフトをハード化出来るとされていたが、それは簡単な処理の場合で難しい処理になってくると言語変換の繰り返しだけではハード化は出来ないだろうと森岡氏。仮にハード化出来たとしても性能が出ない、メモリやロジックが大きくなるなどの問題が出るという。

※画像は森岡氏の講演データ

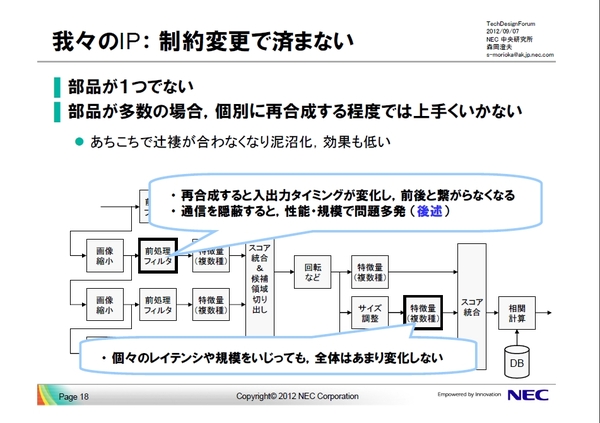

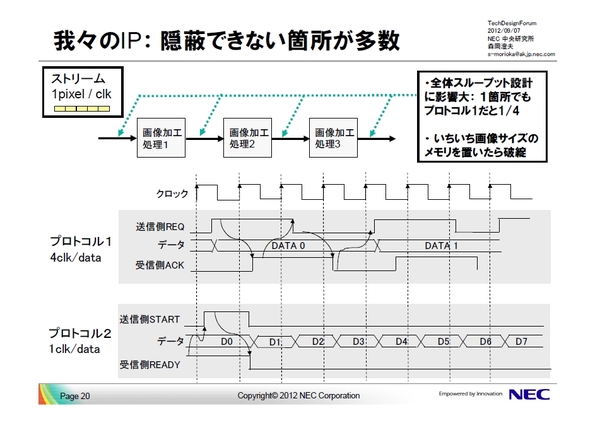

また、制約条件を変えて回路を合成し多機種展開というアプローチも通用しなくなる。部品となるIPが多くなると他の部品との関係性から様々な問題が発生するためだ。更に、現在の高位合成利用で一般的な「通信部分は隠蔽する」というアプローチも限界がある。通信がネックとなる処理の場合、通信を隠蔽してしまうと処理全体のスループットに影響が大きく出るためだ。通信がネックの大量のストリーム・データ処理だとI/Oをサイクル精度で設計しないとスループット達成できないと森岡氏は言う。

※画像は森岡氏の講演データ

更に、これも高位合成利用で良く言われる「演算精度の固定小数点化」。制御が複雑な処理になるとそう簡単に演算精度を解析できなくなってくる。このような数々の問題から、高位合成を用いて目標性能を如何に出すか?という点が問題になってくるため、高位合成を行う前にデータの流し方を考慮したアーキテクチャ設計が必要不可欠になるという。

NECではこのような状況を踏まえ、様々な形で高位合成の活用法の試行錯誤を繰り返した結果、幾つかの独自の「高位合成活用術」を導き出した。

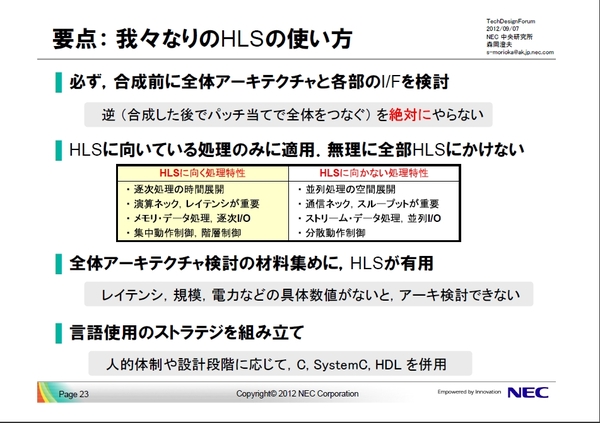

まず高位合成の活用で一番重要なことは、先に述べられた通りアーキテクチャ設計をしっかり行うこと。全体構成を考えずに個々に合成して繋ぐ手法は大体失敗するという経験則から、必ず合成前に全体構成とスループットがクリティカルなI/Fについてはその詳細なタイミングを検討することにした。

また、やみくもに高位合成を使わず、本当に高位合成に向いている処理に使うことにした。例えば、並列処理よりも逐次処理、通信ネックよりも演算ネックなどで、細かな部品単位の合成でその有用性を評価するのではなく、合成した部品を繋げた処理全体のパフォーマンスで高位合成の効果を見るように割り切る事も重要と考えるようになった。

※画像は森岡氏の講演データ

CPS向けに利用する高位合成の選択基準としては、デファクト・ツールであること、FPGAにもASICにも使えること、価格などを重要視し、テクニカルな面では全体アーキテクチャの構成の変更を支援できるという点に重きを置いた。同社では未だ特定の高位合成ツールの利用を決定したわけでは無く、自社開発の「Cyber Work Bench」も含め各種製品を試行している最中だという。

更に森岡氏からはより詳細な「高位合成の使い所」に関する興味深い指摘もあった。

まず、一律にパイプライン合成をかける、合成した回路を単純に並べるだけといった乱暴な事はしない。それは同じような回路が複数個並んでいても処理全体として適切な回路はそれぞれ違うためで、アルゴリズムが複雑になってくるとそういうケースが色々出てくるので注意が必要。高位合成の嬉しさは処理全体のパフォーマンスを上げる事と森岡氏は繰り返し強調した。

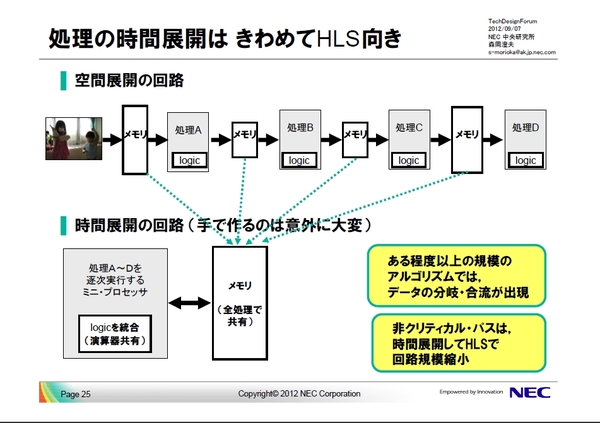

また、高位合成に向いている回路として、「時間展開の逐次処理の回路」を上げ、「これはめちゃくちゃHLS向き」とコメント。演算器やメモリの共有による効果は大きいという。その他、メモリ上で同じデータを繰り返すような処理に対しても高位合成は有効とし、ステートマシンの記述など人出でやるのは大変な処理にこそ高位合成を使うべきとした。

※画像は森岡氏の講演データ

更に、システム全体を見渡して個々の回路に対して個別に合成を指定出来るのが高位合成ツールの良いところで、市販の高位合成ツールにはプラグマとGUIの両方で合成の指定が可能で、物理メモリと論理メモリのマッピングの切り替えがGUI上で簡単に出来る便利なツールもあるという。

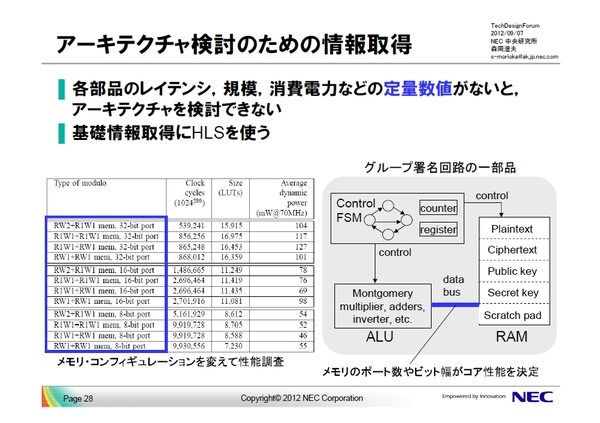

それから森岡氏は以前から唱えている高位合成の活用法として、アーキテクチャ検討における情報収集についても触れた。アーキテクチャを検討するにあたり必要な基礎情報の取得に高位合成を使い、回路のレイテンシ、規模、消費電力などの定量数値を入手する事でより具体的なアーキテクチャ検討が可能になるという。但し、それを行うにあたっては、取得した情報の妥当性を確認することも重要と付け加えた。

※画像は森岡氏の講演データ

最後に森岡氏は、「高位合成が真に必要になるのはCPS時代」と語り、CPS向けのIPには高位合成に適した箇所が多数あり、これまでとは違った視点・考え方での高位合成の利用価値は更に高まるとして講演を締めくくった。

|ページの先頭へ|