HOT TOPIX

AIチップの開発は高位合成で効率化、Mentor「Catapult」によるAIチップ開発事例※訂正あり

2019年3月27日、Mentor Graphicsは品川でプライベート・イベント「IESF 2019 Japan」を開催した。

IESF 2019 Japanは、車載システム開発にフォーカスした技術セミナーで、Mentorによるソリューション紹介と合わせて数々の顧客開発事例が発表された。

ここでは「AIチップ」開発に関するセッションとして行われた、「C++で先端大規模AIチップを開発−Mentorの高位合成ソリューション」について紹介する。

講演者はMentor GraphicsのCalypto製品事業部、山本修作氏である。

山本氏によると、Mentorの提供する高位合成ツール「Catapult」は、AIチップとしてはどちらかと言うとエッジ、端末向けのチップの開発をターゲットとしている。エッジ側のAIチップの多くは、面積、電力、性能(リアルタイム性)など、様々なアプリケーションの厳しい要求に応じるカスタム・ハードウェアであるため、その最適解をいち早く得る上で高位合成を用いた「CtoRTL」手法がはまるという。

特にAIチップの場合は複雑さが半端ではなく、仕様変更も頻繁、今後ますます複雑化していく事を考えると、限られた人員で従来ながらのRTL設計でAIチップを開発するのは困難。高位合成を使っても簡単に作れるものではないが、高位合成を使う事でAIチップの開発を大幅に効率化できると言うのが山本氏の基本的な主張だ。

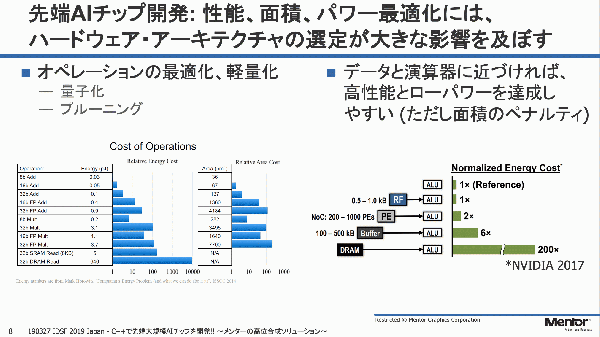

AIチップを開発する上での具体的なメリットとしてまず山本氏が挙げたのは、アーキテクチャの選定。山本氏によると、PPAの最適化に当たっては、量子化、プルーニングなどオペレーションの最適化も重要だが、ハードウェア実装面では演算器とデータの格納先の距離をいかに詰めるかがキー。例えば演算器とデータが近づけば演算スピードやクロック周波数を上げやすく消費電力も抑える事ができるが、その反面メモリによるチップ面積の増大によりチップコストが高くついてしまう。ニューラルネットの処理を考えると、演算性能を取るかメモリを取るかというバランスは非常に重要で、そのトレードオフにおいて高位合成が力を発揮すると山本氏は説明した。

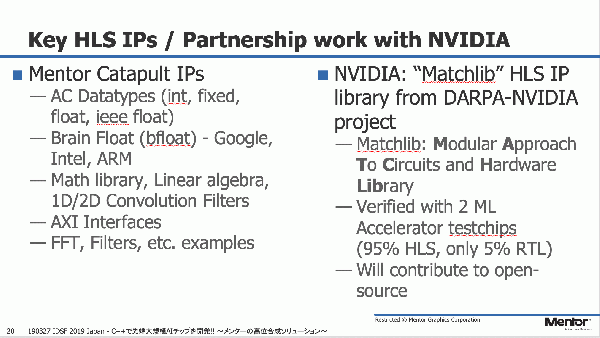

性能、面積、コストのトレードオフという点は「Catapult」に限らず市販高位合成ツールの宣伝文句の定番だが、山本氏によると、Mentorの「Catapult」にはAI処理向けに使える独自のライブラリも用意されている。まず畳み込みニューラルネットワークの畳み込み層の部分は画像処理とほぼ同じで、「Catapult」で用意している画像処理系のIPを利用して設計できる。そのほかに代表的なものとしては、「ACデータタイプ」と呼ぶ任意のビット長に可変な独自のテータタイプや算術演算、線形代数のライブラリがあるほか、Google独自の浮動小数点数フォーマット「bfloat」もサポートしているという。また、「Catapult」のユーザーであるNVIDIAが「Catapult」向けに開発した、「Matchlib(Modular Approach To Circuits and Hardware Library)」というライブラリもあるとの話だ。(MatchilibはNVIDIAがGitHub上で公開している。)

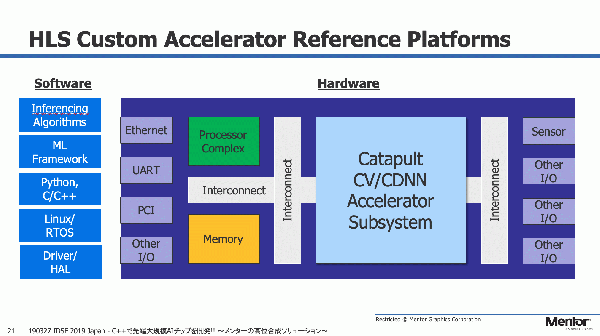

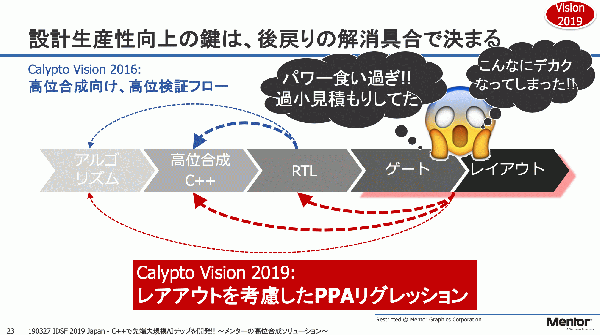

更に山本氏によると、Mentorは「Catapult」を用いたAIアクセラレータ開発用のリファレンス・プラットフォームの提供も計画中で、一般的なカスタムロジック実装向けとPEアレイを並べるタイプの実装向けの2種類のプラットフォームの用意を進めているという。また、「Catapult」の機能強化として、「設計の早い段階でレイアウトを考慮する事で設計の後戻りを解消する」というビジョンの下、PPAリグレッションを前倒しできるような機能を提供する計画との話。これにより従来出来なかったレイアウトを考慮したトレードオフが可能となり、Cのレベルでより詳細にデザインを最適化できるようになるという。

なお、同セッションで山本氏が紹介した「Catapult」を用いたAIチップの開発事例は下記の3つ。Chips&Mediaの事例についてはホワイトペーパーが公開されており、MentorのWebサイトからダウンロード可能との事。

1.FotoNation社

FotoNationはスマートフォン向けの顔認識IPを提供する会社で、IPの出荷実績は30億台以上。同社は次世代の顔認識IPを「Catapult」を用いて設計。Caffeでのニューラルネットワークの実装からFPGAでのハード化まで僅か3週間で完了。当初10fpsだった性能を「Catapult」を用いたアーキテクチャの最適化で30fps(100Mhz動作時)まで向上。RTL設計と比較して設計生産性は4倍、ASIC化に向けたRTLの最適化も容易に完了できた。

2.Chips&Media社

韓国のIPベンダChips&Mediaは、DNN+Deep Learningによる4K/30fpsリアルタイム物体検知IPを「Catapult」を用いて設計。アルゴリズム記述から合成可能なCへの変換を容易に済ませ、工数を掛けずに複数のアーキテクチャを試しPPAを最適化。開発終盤での仕様変更にも容易に対応でき、設計/検証期間を大幅に短縮した。

3.DARPA

DARPA(アメリカ国防高等研究計画局)は、チップ設計の高速化プロジェクト(従来RTL手法の10倍を目指す)においてNVIDIAの提案する高位合成とIPを用いた設計手法を採用。実際にNVIDIAの開発した高位合成用のIP「Matchlib」と「Catapult」を用いて2品種のAIアクセラレータチップを設計。うち1品種はPEアレイを並べるタイプのAIアクセラレータで開発の95%は「Catapult」を利用。従来のRTL設計を行ったのはチップ全体の僅か5%だった。

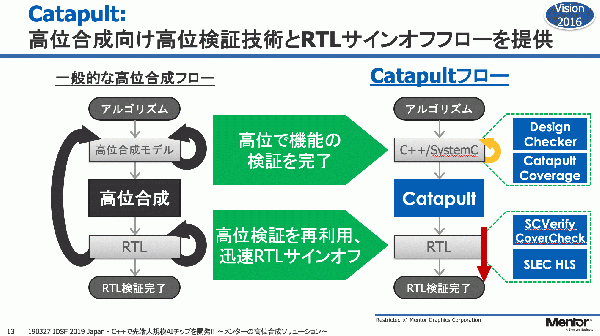

なお山本氏は、「Catapult」を用いた設計生産性向上の鍵となるのは「高位の検証手法」である事を強調。「Catapult」にはそのための検証環境「Catapult DesignChecker」および「Catapult Coverage (CCOV)」が用意されており、RTLではなくCのレベルで機能検証を完了する事が可能。更にその高位の検証環境を利用してRTLでのサインオフ検証を容易に行う環境「SCVerify」、「SLEC HLS」も整えられている。このような強力な検証環境は業界唯一であり、これによって高位合成の能力を最大限引き出せると山本氏は自負していたが、実際に検証はCで閉じて出てきたRTLはワンパスでチェックという手法は「Catapult」ユーザーに高く評価されているという事だ。

※画像は全てMentor Graphics提供のデータ

今回のセッションは時間の関係もあり概要的な説明に終始したが、Mentorは「Catapult」を用いたAIアクセラレータの開発にフォーカスしたセミナー「Mentor AIセミナー」の開催を予定している。(4/16,17と2回開催)同セミナーでは「Catapult」を用いた実践的な設計手法の詳細が紹介される予定。

|ページの先頭へ|