NEWS

【EDSF2011】展示ブースレポート ESLソリューション編

2011年11月16-18日、パシフィコ横浜で開催されたEDSFair 2011Nov に出展していたESL関連ベンダのブース・レポート。

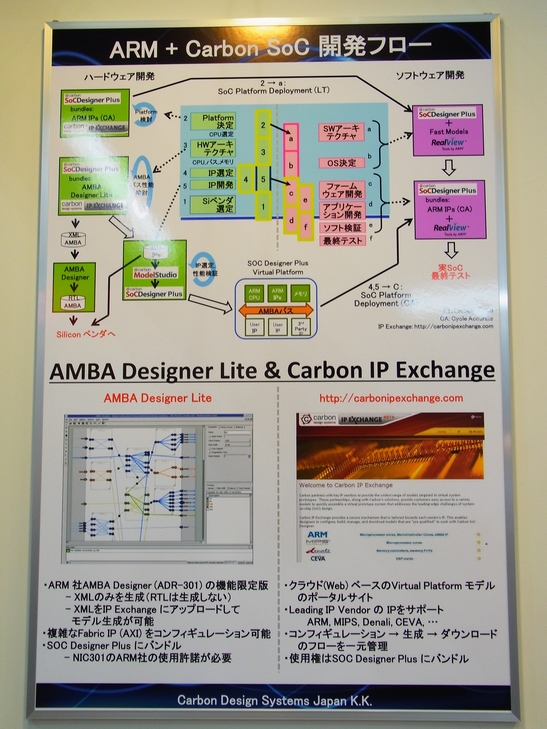

・カーボン・デザイン・システムズ・ジャパン(株)

Carbon Design Systemsは、「Carbon Model Studio」と「Carbon SOC Designer Plus」を展示していた。御存知の通り「Carbon Model Studio」はRTLからバーチャル・プラットフォーム用の100%サイクル精度のSystemC/Cモデルを生成ツールで、「Carbon SOC Designer Plus」はバーチャル・プラットフォームを作成し実行するためのESL環境。「Carbon SOC Designer Plus」は同社がARMから買収したもので、サイクル精度モデルとARM社提供のFastModelsを切り替えながらシミュレーションを実行できるスワップ機能が特徴的と言える。

Carbon Design Systemsは、バーチャル・プラットフォームの普及を妨げる一つの要因である、「各種モデルの流通」にメスを入れた最初のEDA-EXのベンダで、クラウド・ベースのモデル生成サイト「Carbon Model Exchange」を立ち上げ、モデルの容易な供給を目指している。また、将来的にはモデルに限らずバーチャル・プラットフォームそのものをクラウド上で構築し配布するサービスを計画している。

ARMとの密接な関係により、ARMプロセッサ・コアのサイクル精度モデルをいち早く市場に提供している同社は、既にARM Cortex-A15のサイクル精度モデルのリリースを完了済という事で、続いてARMの最新コアARM Cortex-A7のモデル開発にも着手していると聞いた。これら最新のA-15およびA-7のコアモデルが揃えば、ARMの提案する「big.LITTLE Processing」技術を用いたシステムのバーチャル・プラットフォームが構築可能となる。

※画像はCarbon Design Systemsの展示パネル

※Carbon Design Systemsの最新ソリューションについては、セミナー「Verify2011」の講演資料にも紹介されている。

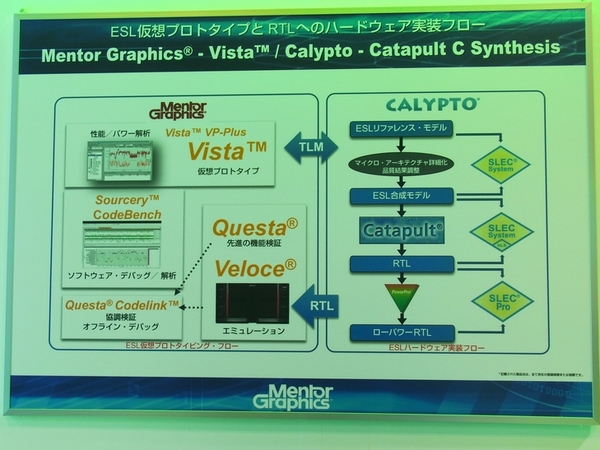

・カリプト・デザイン・システムズ(株)

Calypto Design Systemsは、昨年8月にMentorから高位合成ツール「Catapult C Synthesis」を買収。日本国内では買収後初の展示会出展となり、既存のESL製品と合わせて早速「Catapult C Synthesis」を展示していた。

同社の山本氏ならびにマーケティングVPのShawn McCloud氏(元Mentor Catapultチーム)によると、Calyptoは「Catapult C Synthesis」の買収によりMentorのCatapultチームを全て受け入れ、現在同社の社員数は100名近く。全製品で120社にのぼる顧客を抱えている。聞くところによると、某大手プロセッサ・ベンダもビデオ・グラフィックIPの設計で「Catapult C Synthesis」を適用しTAT短縮を実現しているという事で、同ツールによるテープアウト実績は累計1000件以上。現在、HLS市場のおよそ半分のシェアを占めていると聞いた。

気になるのはCalyptoが「Catapult C Synthesis」を手に入れた事で、何が変わり、何が変わらないのか?という点だが、Shawn McCloud氏によると、Calyptoは既存製品と「Catapult C Synthesis」のインテグレーションを計画中で、まずは「Catapult C Synthesis」と等価性検証ツール「SLEC」をシームレスに接続し、高位合成から高位合成前後の等価性検証のフローをプッシュボタンで実現。更には、低消費電力化ツール「PowerPro」の技術を応用した低消費電力化を考慮した高位合成技術を「Catapult C Synthesis」に実装する予定。

ここまでは想像にたやすい話だが、驚かされたのは「PowerPro」向けにCalyptoが開発したRTL合成エンジンを「Catapult C Synthesis」に移植する計画があるという話。Shawn McCloud氏によると、Calyptoにマージされる前から「Catapult C Synthesis」は合成機能の改善に着手していたが、Calyptoが強力な合成エンジンを持っている事を知り、同エンジンの移植を決定したという事で、CalyptoのRTL合成エンジンは、静的タイミング解析機能や処理速度をワード・レベルとビット・レベルに切り替えて使えるテクノロジ・マッピング機能を備えており、高精度な面積とタイミングの最適化を実現できるという。このエンジンが実装されれば「Catapult C Synthesis」の出力結果に磨きがかかるのは言うまでもない。

尚、変わらない点については、以前からのCadenceやForteとのツール連携に関する取り組みは変わらないという事で、それについては正直疑問が残ると伝えたところ、ツール連携は共通顧客の要望で動いているプロジェクトであり、顧客を裏切るような行為はあり得ないという回答だった。

※画像はCalyptoブースの様子

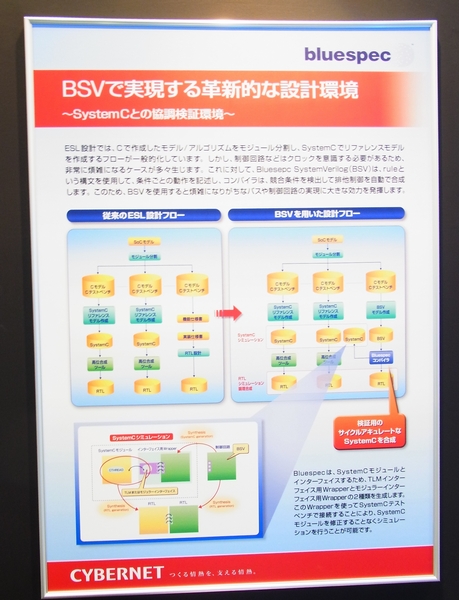

・サイバネットシステム(株)

サイバネットシステムは代理店として販売しているBluspec社のESL合成ツールを展示。

Bluespecは、Bluespec System Verilogという専用言語をベースとする高位合成ツールだが、ここ最近は「SystemC対応」すなわちSystemCとBluespec System Verilogの協調設計手法に力を入れているという事で、「SystemCとBluespec System Verilogで実現する革新的な設計環境の実現」と題した出展社セミナーも実施していた。

Bluespecに関する最近の実績を訊ねたところ、顧客名は明かされなかったが新規顧客を獲得した様子で、来年1月27日に開催予定の「Bluespec User Group Meeting」では新たな顧客採用事例が発表できるはずという話だった。

※画像はサイバネットシステムの展示パネル

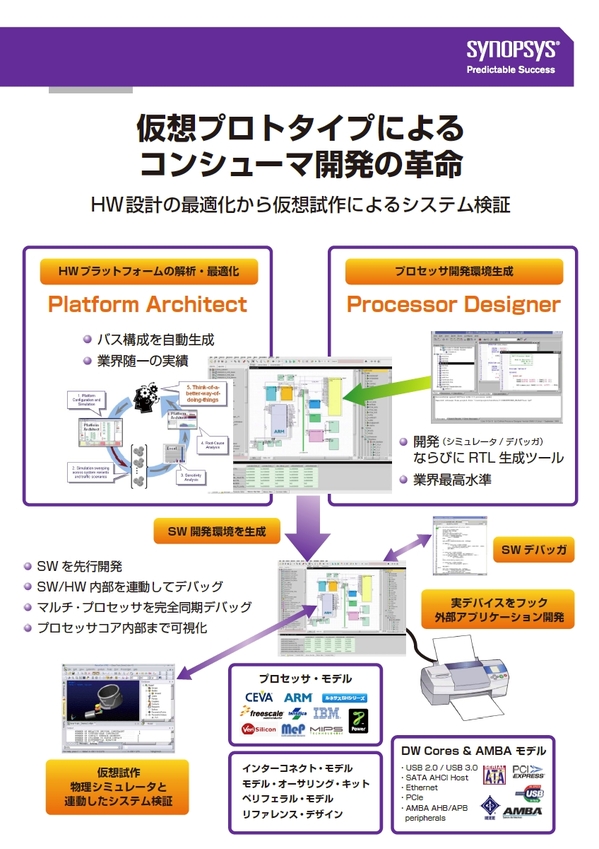

・日本シノプシス合同会社

日本シノプシスのベースでは、ET2011との共催を意識した組込みシステム開発分野に近いEDA製品が展示されていた。中でも目立っていたのがバーチャル・プラットフォーム開発を中心としたESL関連製品群の展示とFPGAベースのプロトタイプ・ソリューション「HAPS」の展示。

ESL製品の展示としては各製品の連携ソリューションの展示が多く、バーチャル・プラットフォーム作成環境「Platform Architect」とカスタム・プロセッサ開発環境「Processor Designer」の連携ソリューションや、複数ESLツールを統合した「Virtualizer」と「HAPS」の連携、アルゴリズム開発環境「SPW」と「Virtualizer」連携などが紹介されていた。

尚、ホットな話題としては、展示会2日目に開催されたET/EDSFair共同企画セッション「ここまで来た!仮想システム開発環境とソフトウェア開発環境」にて、Synopsys米国本社チェアマン兼CEOのAart de Geus 氏が「Virtual Platform Methodology Manual」の発刊をアナウンス。同書籍はタウトル通りバーチャル・プラットフォームを用いたHW/SW開発の指南書で、2012年に発刊される予定。日本語版も登場するという話で、詳細は後日Synopsys社のホームページにアップされるとの事だった。

※画像は日本シノプシスのブースの様子とパネルデータ

・フォルテ・デザイン・システムズ(株)

Forteのブースでは、今年10月にリリースされた高位合成ツール「Cynthesizer」の最新バージョン4.2が展示されていた。

「Cynthesizer」バージョン4.2では、GUIが一新され新たに64ビット環境がサポートされた他、階層設計のサポートやSystemC仮想関数のサポートなども実現された。これら全ては主に日本国内のユーザーからのリクエストに基づいたもので、「Cynthesizer」を使い込んでいる様々なユーザーから寄せられる各種機能強化のリクエストには今後も順次対応していく予定と聞いた。

※画像はForteブースの様子と展示パネル

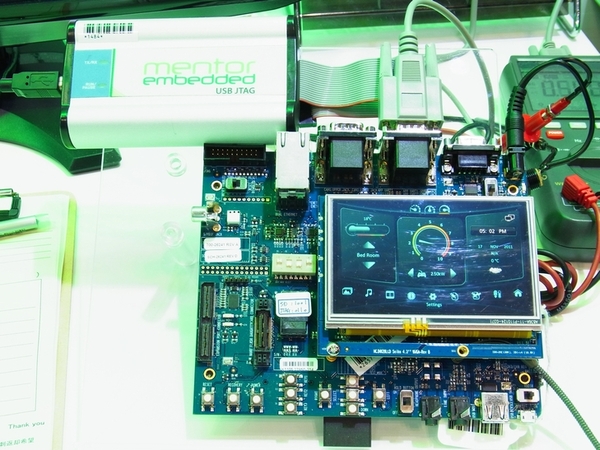

・メンター・グラフィックス・ジャパン(株)

Mentorのブースでは、同社が得意とする組込み向けソリューションの展示が目立っていた。製品として目を引いたのは、組込みソフトウェア統合開発環境「Sourcery CodeBench」、発表間もない新たなRTOS「Nucleus」、UI開発ツール「Inflexion UI」、UMLモデル開発環境「BridgePoint」など。話によると「BridgePoint」は、ETの名物コンテスト「ETロボコン」のスポンサーとして開発支援ツールとして提供され、富士ゼロックスチームなどが使用していたとの事。EDAの世界ではあまり知られていないが、組込み分野ソフト開発におけるモデル駆動開発ツールとして、Mentorに買収される前の Project Technology社時代から知名度が高いようだ。

また、新しいRTOS「Nucleus」について聞いたところ、その特徴は組込みOSとして、より小さなフットプリントを提供できる点、更には内蔵するパワー・マネージメント機能によって、システムの省電力化をコントロールできる点などが挙げられるとの事。ブースでは同RTOSを用いたホーム・システムのデモが展示されていた。

その他、EDA分野の展示としては、Mentorの得意とする物理検証関連よりもESLおよび機能検証関連の展示がメインとなっており、バーチャル・プラットフォーム「Vista」とCalyptoにマージされた高位合成ツール「Catapult」の連携や、それに繋がる「Questa」、「Veloce」といった検証ソリューションが展示されていた。

※画像はMentorの展示パネルとRTOS「Nucleus」のデモの様子

尚、今回のEDSFair 2011 Novは、ET2011との共同開催という事で、ET2011においても幾つかESL関連の展示を行う企業があった。

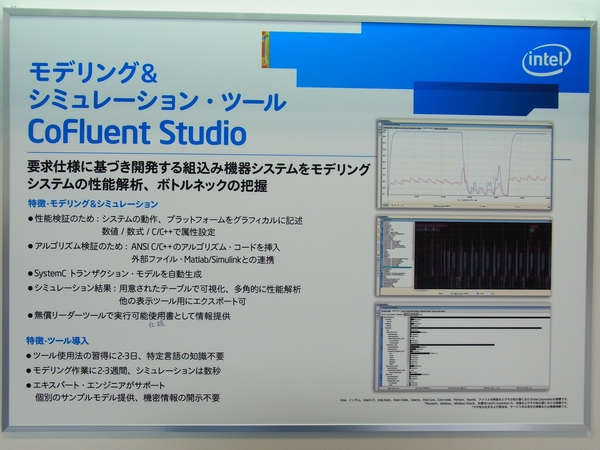

・インテル

インテルのブース内では今年8月にインテルに吸収合併された旧CoFluent社のESLソリューション「CoFluentStudio」が展示されていた。インテル社へ移った元CoFluent社の山下氏に聞いたところ、現在も「CoFluentStudio」は販売が継続されており、これまでと同様の形でライセンスの提供とサポートが行われているとの事。引き続き製品のエンハンスも進められており、バージョンアップも計画されていると聞いた。尚、詳しいところは明らかにされなかったが、「CoFluentStudio」はインテル社内においても製品開発に活用されているようであった。

※画像は「CoFluentStudio」の展示パネル

・日本アルテラ

Alteraのブースでは、ARM搭載のFPGA「SoC FPGA」向けのバーチャル・プロトタイピング・ツール「SoC FPGA Virtual Target」のデモが披露されていた。デモ内容は、「SoC FPGA Virtual Target」上に実装された仮想的なイーサネットI/OとUSB I/Oを使ってシステムを操作するというもので、デモを見たところ動いているバーチャル・プラットフォームは、Synopsys社の「Innovator」のようであった。

Alteraの「SoC FPGA Virtual Target」は、Synopsysとのパトナーシップによって実現されているものであるが、その開発環境はすぐに利用できるパッケージとして、Alteraから顧客に直接提供されるという。

※画像はAlteraブースでの「SoC FPGA Virtual Target」のデモの様子

・富士通セミコンダクター

富士通セミコンダクターは、ESLツールを用いた同社のデザイン・サービス「Cedar?ESL」を展示。その最新技術として、ESL環境とFPGAプロトタイプ・ボードとの連携環境を用いたソリューションを展示していた。

具体的には、バーチャル・プロトタイピング環境としてMentorの「Vista」を使用し、そこにS2C社のFPGAプロトタイプ・ボードを接続。接続にはSpringSoftの「ProbeLink」を利用するというもので、バーチャル・プラットフォームを構築する上でネックとなりやすい、ユーザー固有のロジックや外部からの調達IPなどをFPGAボード上に実装し、そのボードをバーチャル・プラットフォームに接続する事で取り込み、OS/ドライバ/アプリ開発などに役立てるというもの。環境の接続にSpringSoftの「ProbeLink」を用いることで、ボトルネックの可視化も実現できる。

富士通セミコンダクターによると、接続するバーチャル・プロトタイピング環境とFPGAボードは、「ProtoLink」に繋がれば基本的に種類は問わないという事でSCE-MIインタフェースに対応していれば「Vista」や「S2C」以外の環境でも接続可能。ESLサービスとして、これら接続環境を富士通セミコンダクター側が用意してくれるため、顧客はバーチャル・プロトタイピング環境に載せるOSとドライバ、アプリを用意するだけでシステムの仮想シミュレーションを実現できる。尚、展示していたデモでは、S2C社製のFPGAボード上にデジタルメディアプロフェッショナル社製のグラフィックIPコアが実装されていた。

※画像は富士通セミコンダクターの展示パネル。

|ページの先頭へ|