NEWS

EDSF2012で見たEDAベンダ、Aldec,Atrenta,CircuitSutra,Forte,Mentor,その他

2012年11月14-16日、パシフィコ横浜で開催されたEDSFair2012にて訪れた各社のブース、その他聴講したセッションの内容など簡単にレポートします。

今年9月に発表した新製品のFPGAボード「HES-7」を展示。「Virtex-7 2000T」を2個搭載するタイプで2400万ASICゲート相当のデザインに対応できる「HES-7 XV4000」の実物が展示されていた。そのコスト・パフォーマンスの高さから、やはり国内でも引き合い多数との事。海外では既に導入実績が出始めているようだ。

※画像は「HES-7 XV4000」

FPGA設計向けのソリューション「SpyGlass for FPGA」を展示。こちらは始めて耳にしたソリューション。RTLとネットリストでデザイン・ルール・チェックとCDC検証を行う。FPGA設計を狙ったEDAソリューションはにわかに増えてきている。また、「SpyGlass」関連では、TSMCも利用するIPの品質チェック・ソリューション「Atrenta IP Kit」を展示。その他、今年6月に買収を発表したNextOp社のアサーション・シンセシス・ツールも紹介されていた。最近のニュースでは、同社がRTLパワー解析分野で業界2位のEDAベンダになったという発表があった。尚、同社の展示の様子は海外サイト「SemiWiki」でも紹介されていた。

※画像はアトレンタのブースの展示パネル

※関連ニュース

同社は、SystemCのモデリング・サービスに力を入れるインドの設計サービス会社。OCP-IPの提供するツール環境の開発なども手掛けている。日本国内にも複数のクライアントが存在することの事で、日本に限らず北米企業向けにもサービスを展開している。ブースでは、同社が開発した仮想プロトタイピング環境向けのIPパッケージ「Quick Start Package」を紹介。同パッケージはARM Cortex-A9を用いたシステムの仮想プロトタイピングを狙ったもので、SystemC TLMでモデリングされた各種ペリフェラル・モデルがパッケージ化されている。イメージング向けやオーディオ向けなど各種アプリケーションに特化したパッケージを複数用意しているようだ。尚、同社はTLMでモデリングしたIPの単品販売も行なっている。

※画像はCEOのUmesh Sisodia氏

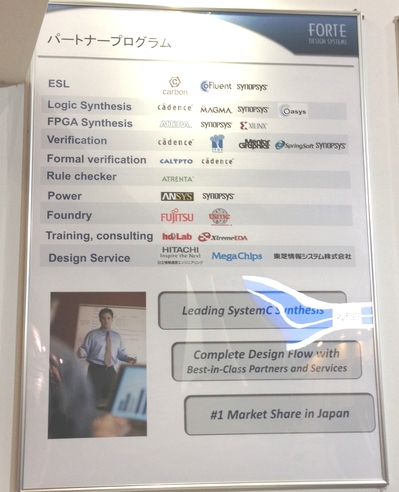

同社は11/14に日立情報通信エンジニアリングによる採用事例を発表。話を聞いたところ、その他にも東芝情報システム、メガチップスも同社の高位合成ツール「Cynthsizer」を以前からデザイン・サービス用に採用しているとの事だった。高位合成ツール「Cynthsizer」は今年8月に新バージョン4.3をリリース。ツールの各種合成機能や解析機能、合成用IPなどのエンハンスが行われたようだ。

※画像はフォルテのブースの展示パネル

※関連ニュース

同社の今年の展示は組込みソフト開発ソリューション、ESLソリューション、自動車向けソリューションに集約。ハードウェア設計関連の主力ソリューションの展示は基本的に無かった。目を引いたのは車載ECUソフトの共通コンポーネント「AUTOSAR」対応の開発環境「Volcanoファミリ」や、組込みソフト統合開発環境「Sourcery CodeBench」関連のソリューション。UMLベースのモデル・ベース開発環境「BridgePoint」なども展示されていた。また、展示会前には、同社の提供する2つのRTOS「Mentor Embedded Linux」と「Nucleus」に関する発表が相次いだ。「Nucleus Innovate Program」に関する発表によると、Mentorは年間売上100万ドル未満の企業に対して、「Nucleus RTOS」と「Sourcery CodeBench」を無償提供するという。

※画像はメンター・グラフィックスのブース

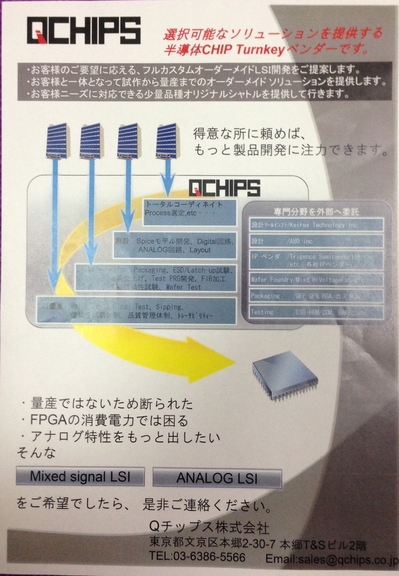

同社は昨年10月に設立されたばかりのLSIターンキー・サービスを手掛けるベンチャー。設計環境のカスタム・サービスや設計サービスを手掛けるケイレックス・テクノロジーと共同でブースを構えていた。社長の内田氏によると、アナログ/ミックスド・シグナルLSIの製造にフォーカスしており、小ロットのニッチなニーズにも細かく対応。顧客の要望に応じて設計サービスにも対応する。使用するファブは海外のファブで、スタートアップながら既に国内顧客からの受注実績もあるという話。ケイレックス・テクノロジーが営業面でサポートしているようだ。

※画像はQチップス社のブローシャ

■Tabula社(株式会社ルネサス・イーストン)

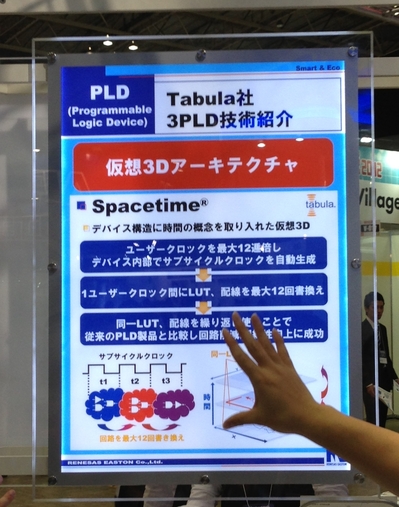

動的再構成技術を用いた「3PLD」を手掛けるTabula社、同社の製品を国内代理店のルネサス・イーストンが併催のET2012で展示していた。Intelの22nmプロセスで製品を出すという事で話題になっている同社は、来年7月に22nmの「3PLD」のESを出す予定との事。「3PLD」は、ユーザー・クロックの最大12倍速でサブ・サイクル・クロックを内部生成。ユーザー・サイクル1回で最大12回の動的回路再構成を実行する。そのパフォーマンスの秘訣は、最大12ポートのマルチ・ポートRAM、最大2GHzのRAM動作速度、最大2GHzの配線切り替え速度にあるとしている。尚、同社の「3PLD」の開発環境は、以前までクラウド上に構築された環境を用いるスタイルであったが、現在ではスタンド・アローンのツールで設計者のデスクトップ上で作業が可能となっていると聞いた。

※画像はルネサス・イーストンの展示パネル

「消費増税よりこっちの方が待った無し!仮想ECU環境を利用した車載ソフトウェアの開発検証!」

セッションの前半部のみを聴講。会場は100名は超えていると思われるかなりの人の入り様であった。日頃耳にする機会の少ない自動車メーカー、サプライヤの仮想ECU環境を用いたソフト開発の取り組みが聞けた。同講演資料の一部は、今年11月に公開されたという、国内のVECU-MBDワーキンググループのホームページからダウンロード可能。同団体は、業界を横断する組織で仮想ECU環境を用いたソフト開発に関する共通のガイドラインの策定を目指している。尚、セッションの前半部を聞いた限りでは、仮想ECU環境を用いた設計手法のネックはやはり「モデルの供給」にあるとの話。これについてはVECU-MBDワーキンググループに参画するSynopsysなどツールベンダーに期待するという声もあったが、マイコン・ベンダが動かなければ話は到底進まない。コンスーマ・エレクトロニクスの世界で仮想ECU環境を用いた開発が浸透しつつあるのは、ARMをはじめとするIPベンダがモデル供給に積極的に協力しているからに他ならない。

|ページの先頭へ|