NEWS

搭載FPGAが変わっただけではなかったSynopsysの新型「HAPS-80」

2015年9月17日、Synopsysは同社のFPGAベース・プロトタイピング・システムの新製品「HAPS-80」のリリースを発表した。

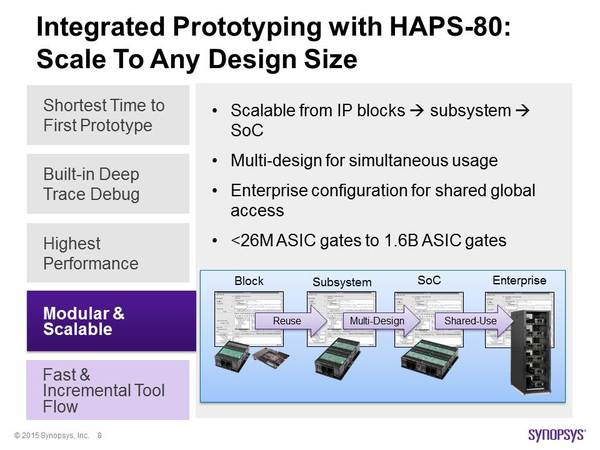

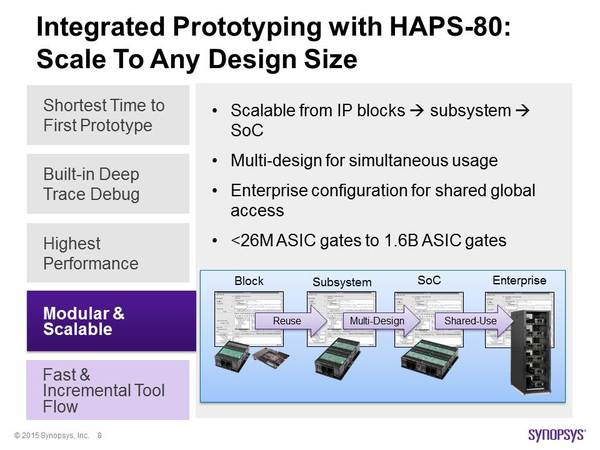

Synopsysによると新型の「HAPS-80」には、Xilinx社の20nm FPGA「Virtex UltraScale VU440」が搭載されており、最小構成のシステムで2600万ASICゲート、最大構成のシステムでは16億ASICゲートのデザインを実装する事ができる。

Xilinxの先端FPGA「Virtex UltraScale VU440」の搭載は、業界において必然的な流れであり、既にAldec,ProDesign,S2Cといった各社が「Virtex UltraScale VU440」を搭載したFPGAベース・プロトタイピング・システムの提供を開始している。

しかし、今回の「HAPS-80」で着目したいのがその最大デザイン容量だ。最大16億ASICゲートとなると、FPGAの個数からしてかなり巨大なボード積層システムになると思われるが、どうやらSynopsysはHAPS用の大型の筐体(ラック)を用意しているようだ。更に「HAPS-80」ではイーサネット接続によるリモート・アクセスが可能となり、「HAPS-80」のリソースを複数の拠点、複数のデザインでシェアしながら効率的に利用できるようになったという事である。こういった大容量のプロトタイピング環境を複数ユーザーで遠隔利用するアプローチは、HAPSの競合であるS2C社も取り組みを進めており、次世代のFPGAベース・プロトタイピング環境の大きな流れになりそうだ。

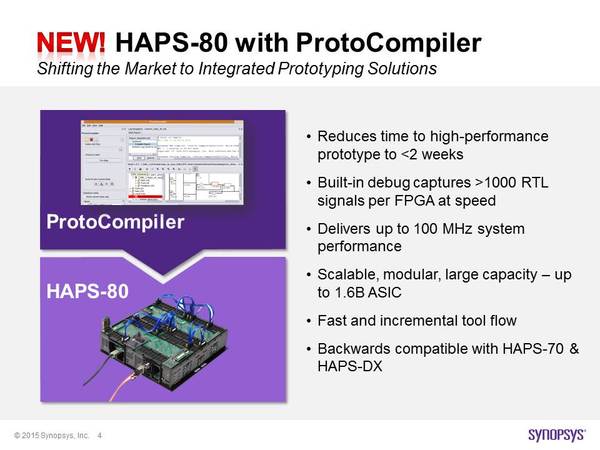

また「HAPS-80」は、昨年リリースされたHAPS向けの新たなソフトウェア環境「ProtoCompiler」によって、デザインのFPGA実装時間、システム性能ともに高速化された。

「ProtoCompiler」はデザインの自動分割実装およびデバッグのためのツールで、2億5000万ASICゲートのデザインを僅か数分で自動分割する事が可能。RTLのコンパイル時間を大幅に短縮できるなどの効果により、プロトタイプ作成までにかかる期間を平均2週間以下に短縮出来るようになったという話である。

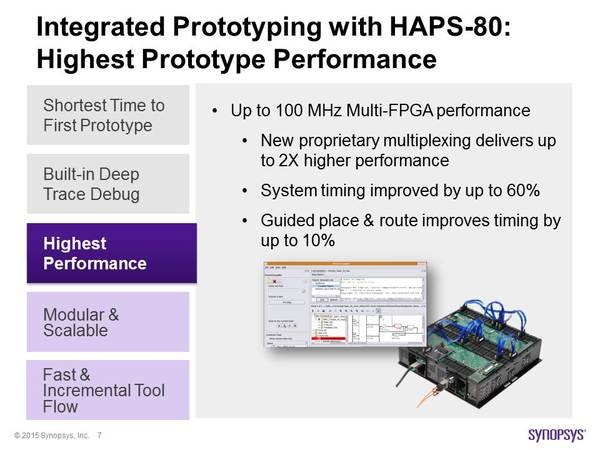

また「ProtoCompiler」を用いることでプロトタイプのシステム性能も大きく向上。「ProtoCompiler」は、新たに改良されたFPGA間通信多重化技術「HSTDM」を活用して、HAPSのハードウェア・アーキテクチャを考慮したマルチプレクシングの自動インプリメントを実行可能で、最大30Mhzのシステム性能を実現。ピン・マルチプレキシングを行わない複数FPGAへのデザイン分割では最大100MHzのシステム性能を実現できるという。

※画像は全てSynopsys提供のデータ

更に新しい「HAPS-80」ではデバッグ機能も強化された。

「HAPS-80」には、デバッグ信号データ抽出機能、デバッグ信号データ格納メモリー、デバッグ専用回路の自動挿入機能が組み込まれており、「HAPS Deep Trace Debug Gen4(DTD4)」と呼ばれるデバッグ技術によって、1つのFPGAあたり1000以上の信号をアットスピードでキャプチャする事が可能。これらデバッグ機能はSynopsysのデバッグ・ツール「Verdi」と統合されており、複雑なデザイン動作をシミュレータ・ライクに短時間で可視化できるため、デバッグ時間を最大50%短縮できるという。

このように今回リリースが発表された新しい「HAPS-80」は、単にFPGAが最新の20nmチップに置き換えられただけでなく、プロトタイプの運用性、システム性能、デバッグ性能など、プロトタイピング環境における重要ポイント全てが刷新され更に強力なソリューションとなった。

このように今回リリースが発表された新しい「HAPS-80」は、単にFPGAが最新の20nmチップに置き換えられただけでなく、プロトタイプの運用性、システム性能、デバッグ性能など、プロトタイピング環境における重要ポイント全てが刷新され更に強力なソリューションとなった。

なお、「HAPS-80」は一世代前の「HAPS-70」との下位互換を維持しており、これまで「HAPS-70」で使用していたシステムやドーター・ボードなどのハードウェア部品を「HAPS-80」で再利用することが可能。「HAPS-80」は既に製品として出荷が開始されている。

|ページの先頭へ|