NEWS

JSNUGレポートその2:エミュレータ「ZeBu」にデジカメSoCを2面実装‐ニコン

2015年9月4日、品川でSynopsysのユーザー・ミーティング「JSNUG 2015」が開催された。

ここでは同イベントで行われた講演の一つ「NIKONはZeBuから何を生み出せるか」について紹介する。

講演者は、株式会社ニコン 映像事業部 開発統括部 第二開発部 第二開発課

高見 亮氏である。

※写真の人物が講演者の高見氏

高見氏はニコンのデジタルカメラ用SoC「EXPEED」の開発に携わる人物で、今回の講演では、「EXPEED」の開発におけるSynopsysのエミュレータ「ZeBu」の適用事例について語ってくれた。

高見氏によると、「ZeBu」の利用を検討するきっかけとなったのは、システム検証のユースケースの拡充で、高機能・多機能化するデジタルカメラのシステムを個別の機能単位ではなくシステム全体で検証したいというニーズがベースとなっていた。

課題としては、システム検証におけるパフォーマンスや予算、運用方法などの他に、社内のESL環境とどのように連携させるかといった点もあり(同社はSynopsysのESL環境Virtualizerも利用している)、まずは「ZeBu」シリーズの最上位品「ZeBu Server-3」の一つ前の世代の製品である「ZeBu Server-1」での評価を開始した。

評価は大きく3つのフェーズで進めた。

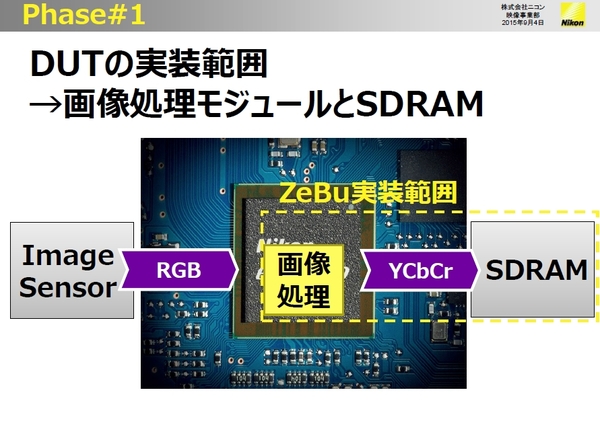

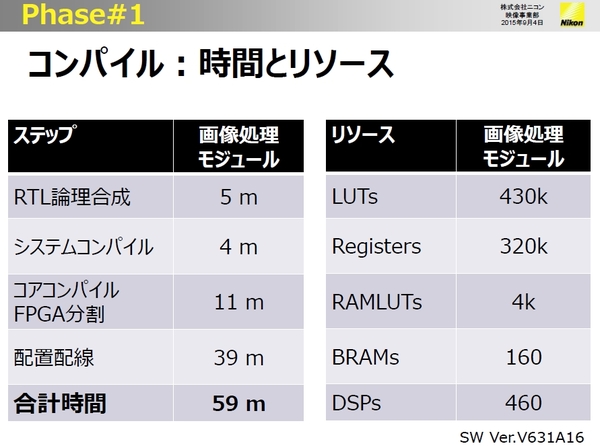

まず最初のフェーズでは「ZeBu Server-1」で画像処理モジュールと外部SDRAMを実装し評価を行った。(同評価対象の回路規模は明らかにされていないが、「EXPEED」自体は数十MGate規模であるとの事。)評価の結果、QVGA画像を用いたテストを含め幾つかのテストにおいて、RTLシミュレーションよりも500倍近く高速だった。同評価におけるコンパイル時間と使用した「ZeBu」上のFPGAリソースは以下の通り。

この評価結果を受けて「ZeBu」のパフォーマンスに満足した同社は、次に製品開発での「ZeBu」適用を目指し、フェーズ2として「EXPEED」全体の実装に取り組んだ。

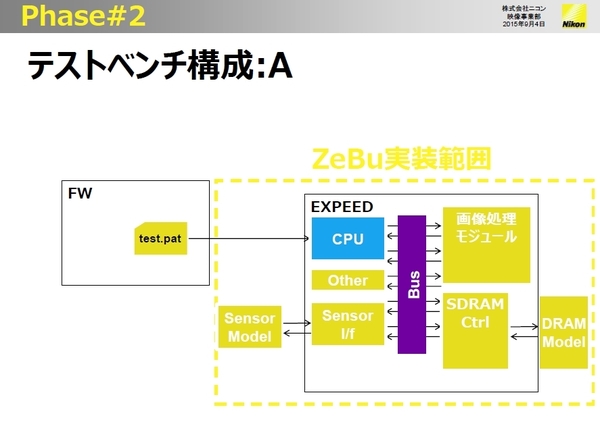

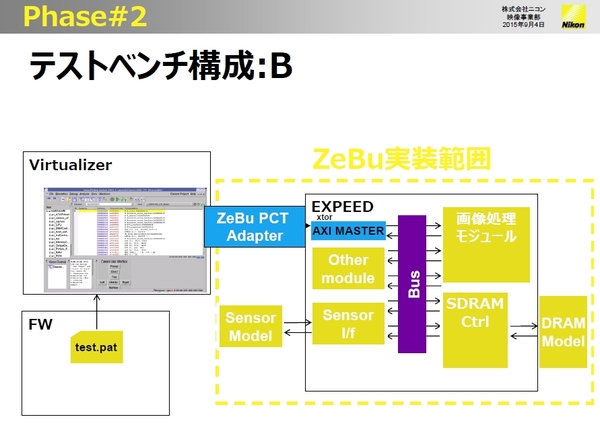

フェーズ2の評価では2種類のテストベンチを構成した。一つは実際のCPUと互換のCPUモデルを用いた構成で、もう一つは互換CPUの代わりに「Virtualizer」を接続した。高見氏によるとファームウェアのデバッグ等においては「Virtualizer」の方が可視化性に優れ使い勝手が良いという事だ。

評価の結果、テスト実行時間はRTLシミュレーション比で概ね200-300倍高速だった。また、テストパターンにおいてメモリへのダンプ/コンペアをオフにすると最大で2倍近く高速化する事が出来るなど、評価を通じてより「ZeBu」を高速化するコツも会得できた。ちなみにバス性能のモニタリング用に「DPI-Cベースのモニター」を利用していたが、これによるテスト実行速度の劣化は無かった。

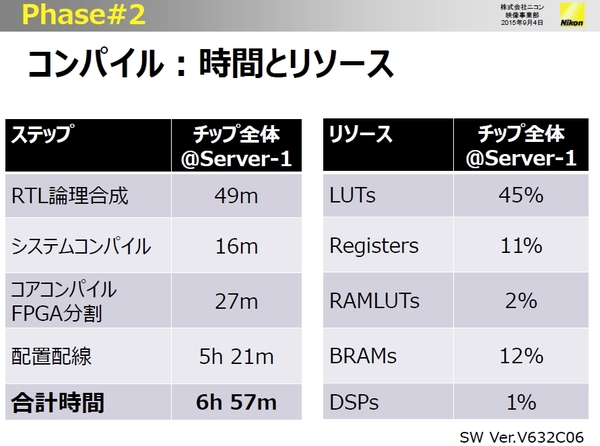

同フェーズ2評価におけるコンパイル時間と使用した「ZeBu」上のFPGAリソースは以下の通り。チップ全体の実装によりコンパイル時間は伸びたが、実用上は問題無いパフォーマンスと判断し、次なる評価フェーズへと進めた。

評価フェーズ3では、更なるパフォーマンス・アップに期待し「ZeBu Server-1」から最新の「ZeBu Server-3」へと環境を乗り換えた。「ZeBu Server-1」がVirtex-5ベースであるのに対し、「ZeBu Server-3」ではXilinxの28nm FPGA Virtex-7 XC7V2000Tがベースとなっている。

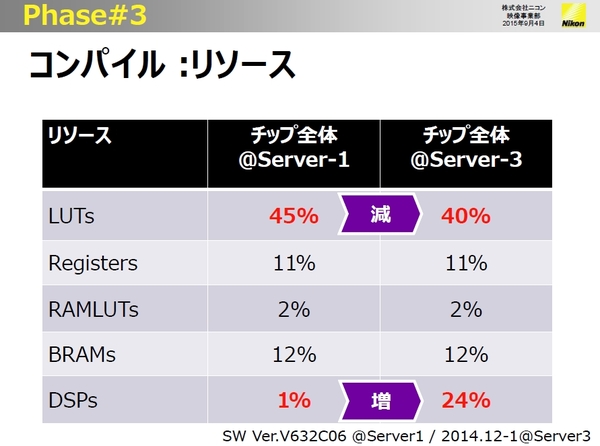

構成は変更せず同じテストベンチを「ZeBu Server-3」に実装したところ、コンパイル時間が約7時間から4時間へと大きく減った。テストベンチ実装に使用するFPGAの個数が減った事で配置配線時間が短縮できた為である。

また、評価にあたり「ZeBu Server-3」ではFPGAのDSPの利用オプションを変更した。「ZeBu Server-1」ではDSPリソースが足りないという判断だったが、「ZeBu Server-3」に搭載されるVirtex-7ではDSPリソースが豊富であったため利用する事にした。これによりFPGAのLUTの使用率が減り、テストベンチを2面分実装する事が可能となった。

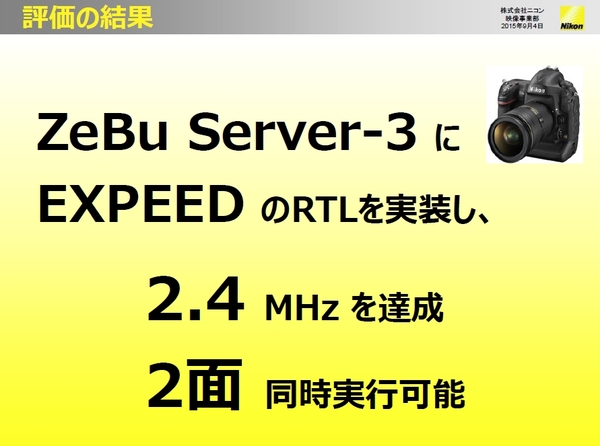

テストの実行時間は「ZeBu Server-1」比で平均して1.5倍の高速化を実現できた。高速化にあたっては、「ZeBu」の機能の一つであるトランザクションベースのDRAMアクセスの利用も効果があった。

これらの評価結果を踏まえ高見氏は、「ZeBu Server-3」は「ZeBu Server-1」の3倍の生産性を実現すると明言。3倍というのは1.5倍の速度向上と2倍のデザイン容量を掛けた結果であり、速度向上もさることながら、テストベンチを2面実装し並行利用できる点が生産性の面で大きかったとの事。また、「ZeBu Server-3」への移行に関しては「ZeBu Server-1」での作業と何ら変わりなく、非常にスムーズに移行できたという事だった。

高見氏は今後の話として、Synopsysの新しい「Unified Compile」にも期待するとして講演を締めくくった。

「Unified Compile」とはSynopsysの各検証ソリューションで共通化される新しいVCSベースのコンパイラの事で、「ZeBu」用にはXilinxと共同開発したバックエンド向けの共通コンパイラが別途用意される予定だ。

|ページの先頭へ|