NEWS

Cadenceが20年振りにテストの技術革新、新型DFTツール「Modus」でSoCテスト時間を最大1/3に

2016年2月3日、CadenceはDFTツールの新製品「Modus」を発表した。

「Modus」は、既存のDFTツール「Encounter Test」の後継にあたる新製品で、Cadence曰く約20年ぶりの大きな技術革新が実現されている。というのも、そもそも既存の「Encounter Test」は2002年にCadenceが買収したIBMの内製EDA技術をベースに開発された経緯があり、約20年に渡り様々な改良が加えられてきたが、今回発表された「Modus」は10種類以上にも及ぶ新たな特許申請技術を取り込み大幅な技術刷新が行われたという事だ。ちなみに「Modus」も既存の「Encounter Test」同様、IBMからCadenceに移ったR&Dメンバーを中心に開発されている。

「Modus」の実現する特筆すべき機能は、デザイン・サイズやカバレッジに影響しない高いテスト圧縮率の実現で、いずれもテスト時間の大幅な短縮すなわちテスト・コストの削減を狙ったもの。それらはフィジカルを考慮する「2D Elastic Compression」アーキテクチャと呼ばれる同ツールの新たなアーキテクチャーによって実現されている。

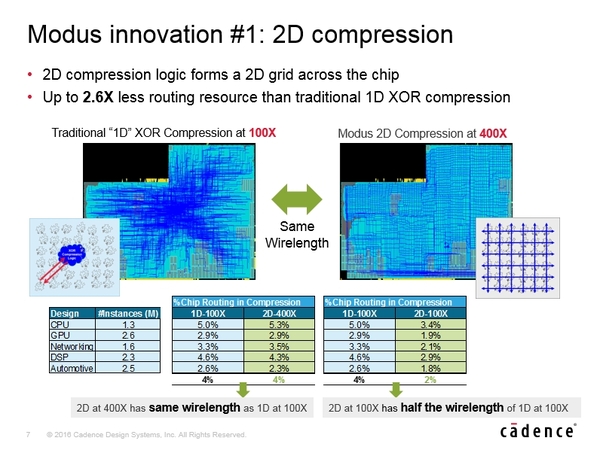

「2D Elastic Compression」は、「2D Compression」機能と「Elastic Compression」機能の2つの機能で成り立っており、「2D Compression」機能は同社の論理合成ツール「Genus」と組み合わせて利用する事でフィジカルを考慮しながらテスト回路を挿入する事が可能。これによりフィジカルを考慮しない場合よりもテスト回路の配線長を最大60%以上短くできる。一般的に利用されているXOR圧縮手法では圧縮率を上げると配線長が伸び配線リソースに大きな影響が及んでしまうが、「Modus」を利用すれば配線リソースへの影響を抑えつつ高いテスト圧縮率を実現できる。

Cadenceの示す評価データによると、従来手法で100倍の圧縮率の場合と「2D Compression」を用いた400倍の圧縮率の場合で配線長はほぼ同一。同じ圧縮率の場合は「2D Compression」を用いる事で配線長を半減できたという事だ。

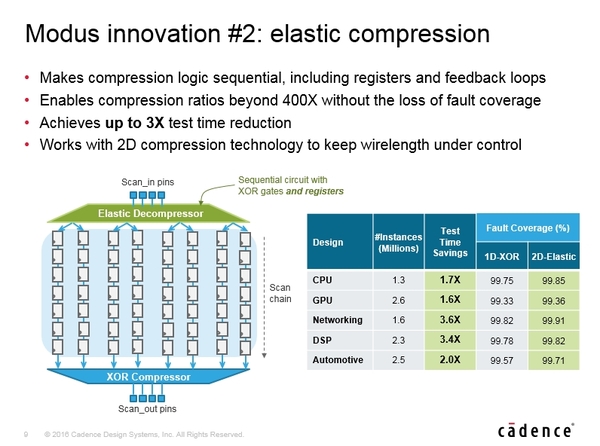

もう一つの「Elastic Compression」機能は、論理合成ツール「Genus」との組み合わせに関わらず利用できる機能でデコンプレッション・ロジックに対してレジスタやフィードバック・ループを組み込むもの。これによりATPG実行中に複数のスキャンサイクルをまたいだケアビットのコントロールが可能となり、従来手法よりも高い故障検出率を実現できるようになる。別の言い方をすると、従来、テスト圧縮率を上げると低下する傾向にあった故障検出率を高い圧縮率でも維持できるようになる。

Cadenceはこの「2D Compression」機能と「Elastic Compression」機能の2つの機能を組み合わせる事で、テスト時間を最大1/3までに削減できるとしており、既に同ツールを利用している先行ユーザーからはテスト時間を40-70%削減出来たという複数のコメントが寄せられている。

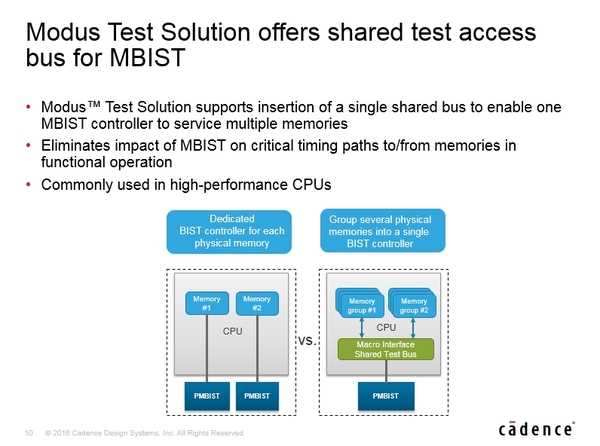

なお、「Modus」ではメモリBISTの機能として、組み込みメモリバスを用いて一つのBISTコントローラで複数のメモリを扱えるような機能もサポートされているとの事。

Cadenceは新製品「Modus」の正式出荷を今年の3月末-4月上旬に予定している。

|ページの先頭へ|