NEWS

Cadenceがリリース25周年のアナログ・カスタム設計環境「Virtuoso」を大幅強化

2016年4月6日、Cadenceは同社の旗艦製品の一つアナログ・カスタム設計環境「Virtuoso」プラットフォームのバージョンアップを発表した。※訂正あり

Cadenceが初のアナログ設計ツール「Analog Artist」をリリースしたのが1991年で、以降、同ツールをベースに確立されたアナログ・カスタム設計環境「Virtuoso」プラットフォームは今年で25周年を迎える。この25周年を記念して、Cadenceは今年「Virtuoso」のプロモーションに力を入れており、今回発表したバージョンアップはその大きな目玉として扱われている。

「Virtuoso」最新バージョン6.1.7では、同プラットフォームを構成するアナログ設計環境「Virtuoso ADE」が検証技術を中心に刷新され、レイアウト環境「Virtuoso Layout Suite」が大幅に機能強化された。

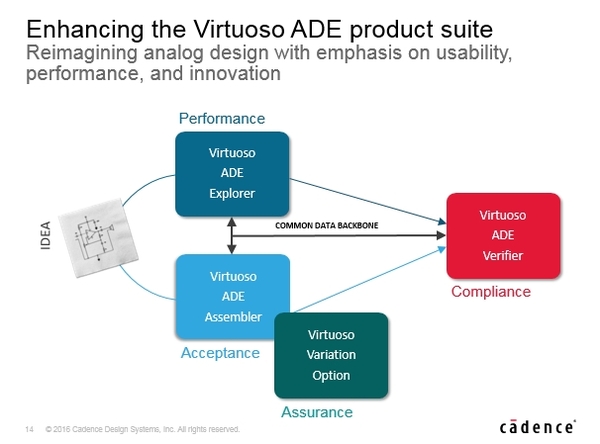

まず、アナログ設計環境「Virtuoso ADE」においては、次世代の製品ラインナップとして下記スライドの通り3つの新製品と1つのオプション機能が追加された。従来の「Virtuoso ADE」は、L,XL,GXLと製品の機能に応じて3種類のグレードが用意されていたが、新たに追加された各製品はそれぞれ独立した機能を担うものとなっている。

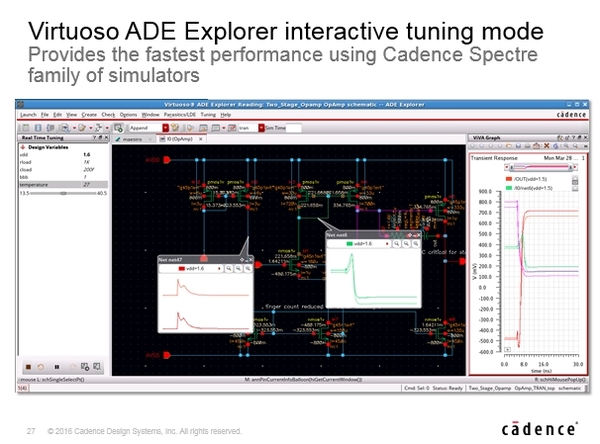

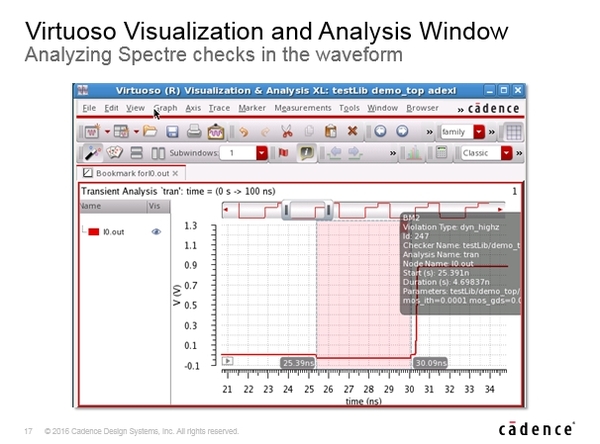

「Virtuoso ADE Explorer」は、アナログ回路の設計初期においてシングルテストベンチのコーナーケース・シミュレーションを行う環境で、オンメモリーでネットリストを再構築せずに回路のチューニングを行う事ができる「Interaractive device tuning mode」という機能を備えている。同機能を利用すれば、例えば回路の抵抗の値を変えた際の特性の変化(波形の変化)を瞬時に確認できる。(バックグラウンドでシミュレータSpectreが動いている)また、回路図上にワンクリックでノードの波形を示したり、アサートチェックや耐圧チェックなどの各種チェックをGUIベースで実施できるなど、ツール全体でグラフィカルな形で対話的かつ直感的な作業が可能となっている。

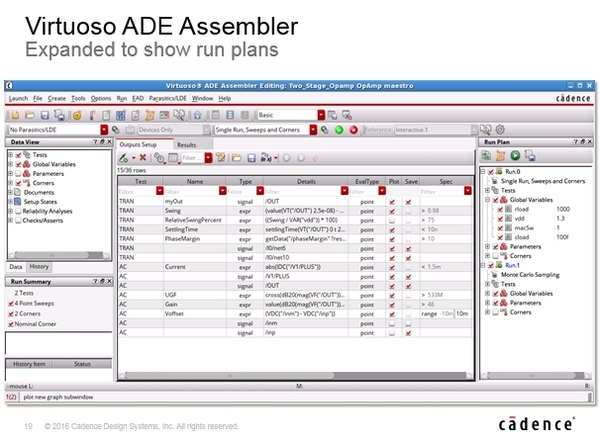

「Virtuoso ADE Assembler」は、マルチテストベンチの環境で、「Virtuoso ADE Explorer」で検証した回路を様々な入力や条件設定によってまとめてチェックする事ができる。検証のシナリオをGUIベースで簡単に管理できる機能を備えており、「Virtuoso ADE Explorer」と同じくグラフィカルな形で対話的かつ直感的に検証の順序や制御を細かく指示できる。

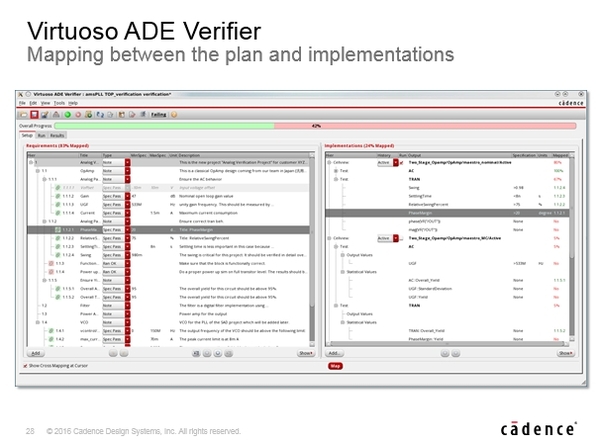

「Virtuoso ADE Verifier」は、「Virtuoso ADE Explorer」および「Virtuoso ADE Assembler」の検証結果を総合的に可視化する検証コックピットとしての環境で、複数の設計者のテストの項目や進捗を統合的に管理することができる。また自動車の機能安全規格ISO26262をはじめとする各種産業界の規格に対応する機能が備えられており、規格に準じたレポーティングなども「Virtuoso ADE Verifier」で対応可能だという。

なお、オプション機能「Virtuoso Variation Option」は、従来の「Virtuoso ADE GXL」に備えられていたものと同様の機能となる。

※画像は全てCadence提供のデータ

Cadenceが今回「Virtuoso ADE」の検証機能を大幅に強化した背景としては、自動車業界を中心とするトレーサビリティに対する要求やアナログ回路のより高精度な検証要求に対応するためで、ここ数年自動車業界でキーワードとなっている機能安全規格ISO26262が一つの大きなトリガーとなっている話だ。

ちなみに「Virtuoso」最新バージョン6.1.7では同ツール初の日本語対応がなされているという事だが、この辺りは日本の自動車業界を強く意識した対応と見て取れる。

アナログ検証環境と合わせて強化された「Virtuoso Layout Suite」は、L,XL,GXLという製品構成を維持しているが複数の機能強化が施されている。

まずレイアウト・エディタのエンジン・アルゴリズムが刷新され描画速度が10倍から100倍高速になった。これは同社の新たな特許技術によって実現されているという話で、エディタの高速化は設計者にとってはシンプルだが非常に大きなメリットと言える。また「Dynamic Measurement」と呼ばれる自動計測機能なども新たに用意された。

更にレイアウト関連の機能としては、回路の階層構造とレイアウトの階層構造を一致させる「階層制御」の機能が用意されたほか、「ModGen」と呼ばれる素子の自動配置機能が強化された。「ModGen」を利用すればインタラクティブかつ高速に指定したルールに沿って素子をアレイ化して自動配置する事が可能になるという。また、同じく新機能として追加された「pin-to-trunk」という機能は、電流の流れをみて「賢く自動配線」するものでアナログ回路に有効。配線の生産性を最大50%向上出来るほど効果があるという。

以上、上述した通り今回の「Virtuoso」のバージョンアップはかなり大掛かりなものとなっており、「Virtuoso」プラットフォーム全体としての従来比10倍相当の性能向上を実現しているという話。先頃競合のSynopsysが新製品を投入したばかりだが、アナログ/カスタム設計環境の移行は同一ツールのバージョンアップでもかなりの時間と労力を要する事を考えると、これまでCadenceが築き上げてきた「Virtuoso」の牙城は今回の大幅な機能強化でより強固なものになるのかもしれない。

|ページの先頭へ|