NEWS

Achronixが機械学習および広帯域ネットワーキングアプリケーション向けの新型7nm FPGAファミリを発表

2019年5月21日、SoC組み込み型FPGAを手掛けるAchronixは、新しいFPGAファミリ「Speedster7t」を発表した。

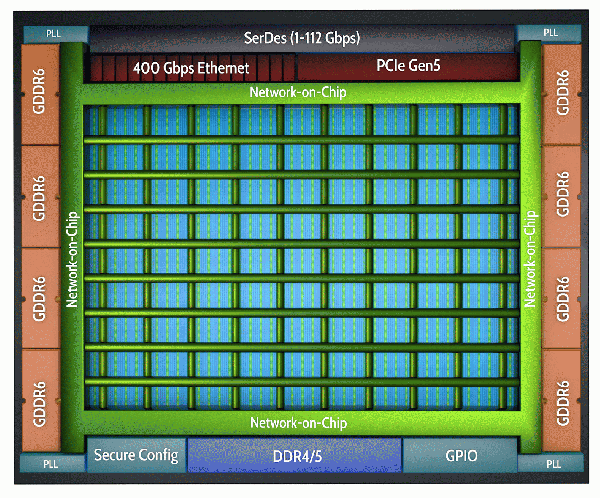

発表によると「Speedster7t」は、TSMC 7nm FinFETプロセスで製造されるスタンドアロンのFPGAで、機械学習および広帯域ネットワーキング・アプリケーション用に最適化された新しいアーキテクチャーをベースとしている。同アーキテクチャーの特徴は以下の通り。

・新しい2Dネットワークオンチップ(NoC)

データトラフィックをFPGAファブリック全体に水平方向と垂直方向に分散。NoCの各行または各列は、各方向に512Gbps相当の速度でデータを転送できる。(各行/列は2x256ビット,単方向のAXIチャネルとして実装されている)

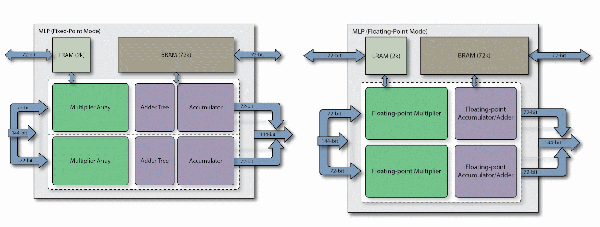

・高密度の新しい機械学習プロセッサ(MLP)を搭載

MLPは最大32個のMACを備えたコンフィギュラブルな演算ブロック。4から24ビットの整数型とBfloat16を含む様々な浮動小数点モードをサポート。MLPブロックとエンベデッド・メモリブロックの緊密な結合によりFPGA配線に伴う遅延を無くし、機械学習アルゴリズムを最大周波数750MHz、61.4TOPSで実行できる。※最大構成でMAC数40,960個(int8)の場合

・最大8個のGDDR6コントローラ、4Tb/s以上のメモリ帯域幅を提供。

HBMベースのFPGAと同等のメモリ帯域幅を数分の1のコストで提供可能。

・PCIe Gen5 2x16, Ethernet 32レーン, 8x400G

・6入力LUT 最大 260万個

・オンチップ・メモリ最大 300Mb

※画像は全てAchronix web上のデータ

Achronixは、FPGAのプログラマビリティとASICの配線構造およびコンピューティング・エンジンを融合させた新たな「Speedster7t」のアーキテクチャーは、既存のFPGAの上を行く「FPGA+」クラスのテクノロジを生み出すとしている。

「Speedster7t」のSampleチップと評価用ボードは、2019年第4四半期に発売される予定。

|ページの先頭へ|