NEWS

Siemensが新型エミュレーターと合わせてFPGAプロトタイピング・システムを投入

2021年4月21日、Siemensはハードウエアベースの検証ソリューションとして3種類の新製品を発表した。

※この発表は3月26日にSiemensが発表したものをあらためて傘下のメンター・グラフィックス・ジャパンを通じて発表したものとなる。

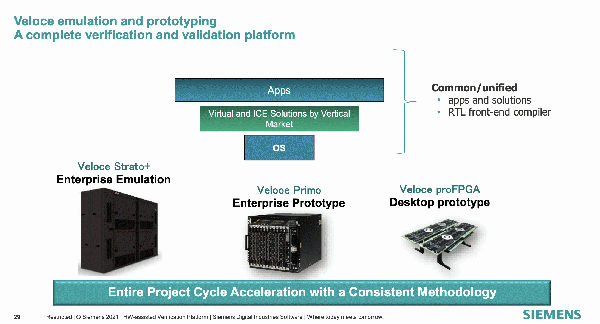

今回Siemensが発表したのは、エミュレーターの新型製品「Veloce Strato+」、FPGAベースのプロトタイピング・システム「Veloce Primo」および「Veloce proFPGA」の3製品。「Veloce Strato+」は既存エミュレーターの後継製品で、「Veloce Primo」および「Veloce proFPGA」はSiemens(Mentor)として初のFPGAプロトタイピング・システムとなる。

「Veloce Strato+」は「Crystal 3+」と呼ばれるSiemensの独自の2.5Dチップ(恐らく16nmチップ)が搭載され、デザイン容量は既存の「Veloce Strato」の1.5倍に拡張された。Siemensは、「Veloce Strato+」のデザイン容量は市場トップの150億ゲートを実現し、デザインのコンパイル速度、実行速度は業界最速だとしている。

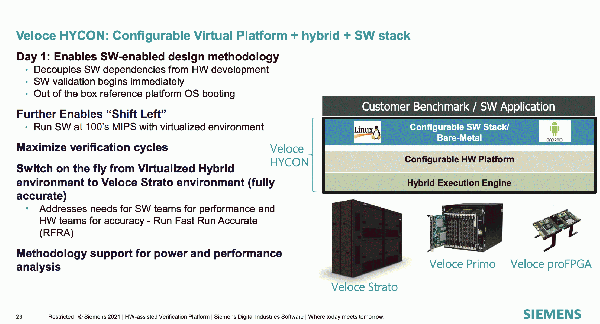

また、今回「Veloce Strato+」のリリースに合わせて、「Veloce HYCON(HYbrid CONfigurable)」と呼ばれる仮想プラットフォームが新たに用意された。同環境上で仮想プロセッサモデルを実行することが可能で、ソフトウェアの早期検証や「Veloce Strato+」と接続したハイブリッド・エミュレーションが可能になる。

なお、「Veloce Strato+」と「Veloce Strato」はシャーシが同じでボードを差し替えるだけで既存システムのグレードアップが可能。「Veloce Strato」のユーザーとして知られるAMDは、第2世代および第3世代のEPYCプロセッサーの開発で「Veloce Strato」を利用しており、「Veloce Strato+」も先行導入しているという。

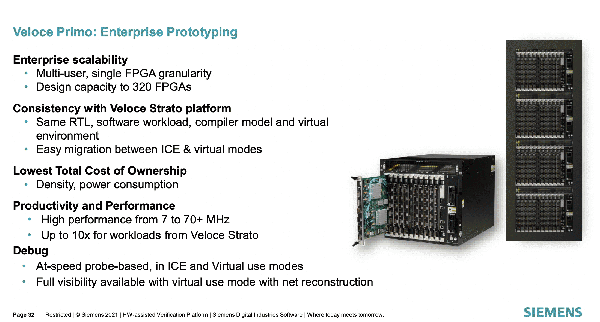

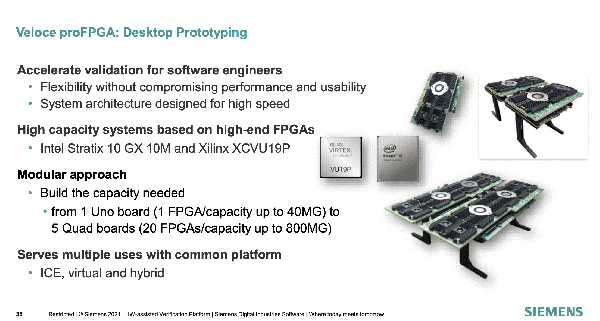

「Veloce Primo」と「Veloce proFPGA」はいずれもXilinxの16nmFPGA「Virtex UltraScale+ VU19P」を搭載するプロトタイピング・システムで、「Veloce Primo」はエンタープライズ向け、「Veloce proFPGA」はデスクトップ向けという位置付け。大型シャーシに最大10枚、計320個のFPGAを搭載できる「Veloce Primo」は最大80億ゲートのデザイン容量を誇り、実行速度は最大70Mhzに達するとされる。「Veloce proFPGA」の方は独ProDesignよりOEM供給される製品で、1つのボードに最大4個のFPGAを搭載可能。ボードを5枚連結することで最大8億ゲートのデザインに対応できる。

※画像はSiemens提供のデータ

どちらのプロトタイピング・システムもフロントエンド環境が「Veloce Strato+」と同じであるためエミュレーターからのデザイン移行が容易であり、同じRTL、同じ仮想環境、同じトランザクター/モデルを使用してシステム検証を実行可能。Siemensは、仮想環境、エミュレーター、FPGAベース・プロトタイピングと三位一体となった包括的な検証環境により、より高度・高速な検証、検証サイクルの短縮が実現できるとする。

ここのところCadence,Synopsysと新型エミュレーター/FPGAプロトタイピング・システムの発表が相次いでいるが、その背景にはチップの大規模化に伴う高速・大容量な検証ソリューションへのニーズの高まりがある。これまでエミュレーターの分野ではCadenceとSiemens(Mentor)の2社が競い合ってきたが、そこにFPGAベースのプロトタイピング・システムも加わることで、同分野のシェア争いはSynopsysやS2Cなど他のベンダも含めてより激化していくことだろう。

|ページの先頭へ|