NEWS

GraphcoreがTSMCの3D技術でAIプロセッサを40%高速化、スパコン開発計画も発表

2022年3月3日、データセンター向けのAIプロセッサを手掛ける英Graphcoreは、新型のAIプロセッサ「Bow IPU」を発表した。

IEEE Spectrumの記事:Graphcore Uses TSMC 3D Chip Tech to Speed AI by 40%

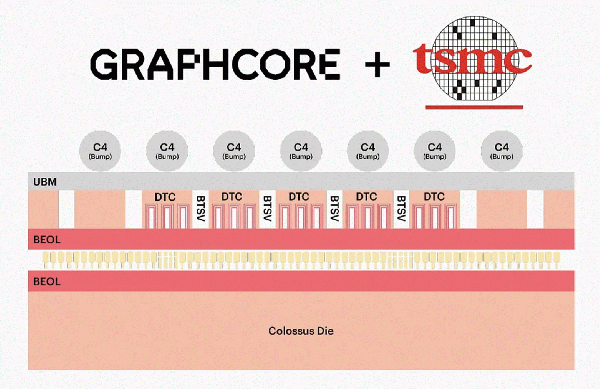

発表によるとGraphcoreの新製品「Bow IPU」はTSMCの3D技術「Wafer-on-Wafer」を用いた市場初の商用チップで、同チップのベースとなっている「Colossus MK2 IPU」と同じTSMCのN7プロセスを用いて製造されている。「Wafer-on-Wafer」は文字通り2枚のウエハを貼り合わせて3Dダイを作る技術で、Graphcoreはこの技術を電力効率の最適化と電力供給の向上をウエハレベルで実現するために利用した。

Graphcoreによると、2枚のウエハのうち片方はAI処理用のプロセッサ・ダイで既存の「Colossus MK2 IPU」と同一、もう一方のウエハは電源供給ダイを搭載したウエハでコンデンサと「BTSV」と呼ばれる新しいタイプのシリコン貫通ビアが詰め込まれており、それらによりプロセッサ・ダイへ直接的かつスムーズに電力供給が行われる。その結果プロセッサ・コアがより低い電圧でより高速に動作できるようになるため、「Bow IPU」と「Colossus MK2 IPU」は中身は同じプロセッサでありながら動作速度が1.85GHzに向上、性能は最大40%、電力効率は最大16%高められるという。

※画像はIEEE Spectrumの記事より引用

特筆すべきは、ユーザーはソフトウェアの変更を一切変更することなく「Colossus MK2 IPU」から「Bow IPU」に移行できる点で、Graphcoreは電源供給ダイを追加してアップグレードした「Bow IPU」を元の「Colossus MK2 IPU」と同じ価格で販売している。「Bow IPU」を搭載するシステム「Bow Pod」は256チップ搭載の「Bow Pod-256システム」で89ペタフロップス、1024チップ搭載の「Bow Pod-1024」で350ペタフロップスの演算能力を提供する。

なおGraphcoreは今後の計画として、ニューラルネットワークに数百兆のパラメーターを持つ「脳規模」のAIをトレーニングできるスーパーコンピューターを構築することを発表。英国の数学者Jack Goodにちなんで名付けた「GoodComputer」は、8,192の「Bow IPU」を備えたシステムで10エクサフロップスを超える性能を実現。(富嶽のピーク性能が1.5エクサフロップス)同製品は2024年に納品予定でそのコストは約1億2,000万米ドルになる見通しだという。

|ページの先頭へ|